## POLYTECHNIC, B.E/B.TECH, M.E/M.TECH, MBA, MCA & SCHOOL

Notes Syllabus Question Papers Results and Many more... Available @ www.binils.com

Reg. No.: Question Paper Code: 50485 B.E./B.Tech. DEGREE EXAMINATIONS, APRIL/MAY 2023. Third/Fourth Semester Electronics and Communication Engineering EC 8392 - DIGITAL ELECTRONICS (Common to: Biomedical Engineering/Computer and Communication Engineering/Mechatronics Engineering/Medical Electronics/Robotics and Automation) (Regulations 2017) Maximum: 100 marks Time: Three hours Answer ALL questions.  $(10 \times 2 = 20 \text{ marks})$ equivalent of (374.26)8 and the hexadecimal (782.256)10. Simplify the expression F = (AB + CD)[(A' + B')(C' + D')]Show a full-adder can be converted to a full-subtractor with the addition of an 3. inverter. What is Decoder? Show that a decoder with enable input can function as a 4. demultiplexer. Differentiate Mealy and Moore state machines. Construct T flip-flop with D flip-flop. 6.

Define static and dynamic hazard.

Differentiate EAPROM and EEPROM.

What is the advantage of ECL logic family?

Define primitive flow table.

## POLYTECHNIC, B.E/B.TECH, M.E/M.TECH, MBA, MCA & SCHOOL

Notes Syllabus Question Papers Results and Many more...

www.binils.com

Available @

## PART B — $(5 \times 13 = 65 \text{ marks})$ 11. (a) (i) Realize the function F = (AB)' + A + (B+C)' with minimum number of NAND gates only. (ii) Using the Karnaugh map method obtain the minimal sum of the products expression for the function $F(A, B, C, D) = \sum (0, 2, 3, 6, 7) + d (8, 10, 11, 15).$ (b) Using the Quine-McClusky method, obtain the minimal sum of the products expression for the function $F(A, B, C, D) = \sum (1, 3, 4, 5, 9, 10, 11) + \Phi(6, 8).$ Design a 4-bit Carry look-ahead adder and explain how it reduces the (a) carry propagation delay time over Ripple Carry adder. Implement the full adder circuit using two 4:1 multiplexers. Derive the expressions for implementing 4-bit magnitude comparator. sequential circuit has two J-K flip flops, A and B, and one input x described by the following flip-flop equations. JA = BJB = x'KA = Bx' KB = A'x + Ax'Obtain the state equations, derive the state table for the circuit and draw the state diagram. Or (b) Design a synchronous counter that count the following sequence 0, 2, 3, 5, 7, 10, 12, 15, 0, 2 etc. Use J-K Flip-flops. 14. (a) Design an asynchronous sequential circuit with two inputs X and Y and with one output Z. Whenever Y is 1, input X is transferred to Z. When Y is 0, the output does not change in X. (b) Discuss about critical race, noncritical race and cycle in asynchronous sequential circuits with examples. 50485 2

## POLYTECHNIC, B.E/B.TECH, M.E/M.TECH, MBA, MCA & SCHOOL

Notes Syllabus Question Papers Results and Many more... Available @

www.binils.com

(i) SRAM and DRAM

(7)

(ii) PLD and FPGA

(6)

Or

(b) Explain the purpose of totem pole at the TTL output configuration. Why should the totem pole outputs not be tied together to form wired logic? Explain with the circuit diagram.

PART C —

$$(1 \times 15 = 15 \text{ marks})$$

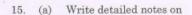

(a) A sequential circuit has one input and one output. The state diagram is shown in Figure. 16(a). Design the circuit with JK flip-flops.

(b) Implement the following Boolean functions with PAL and obtain PAL program table

$F_1(A, B, C, D) = \Sigma(2, 12, 13)$

$F_2(A, B, C, D) = \Sigma(7,8,9,10,11,12,13,14,15)$

$F_3(A, B, C, D) = \Sigma(0,2,3,4,5,6,7,8,10,11,15)$

$F_4(A, B, C, D) = \Sigma(1, 2, 8, 12, 13).$

3

50485