## POLYTECHNIC, B.E/B.TECH, M.E/M.TECH, MBA, MCA & SCHOOL

Notes Syllabus Question Papers Results and Many more...

www.binils.com

Available @

|                    | Reg. No. :                                   | Minu est sue      |                |          |

|--------------------|----------------------------------------------|-------------------|----------------|----------|

|                    | uestion Paper C                              | ode : 3014        | 18             |          |

|                    | uestion ruper e                              | /en//eMeMes       | MacMacM=1      |          |

| B.E./B.            | Tech. DEGREE EXAMIN                          | ATIONS, APRIL     | /MAY 2023.     |          |

|                    | Third Sen                                    | nester            |                |          |

|                    | Electrical and Electro                       | nics Engineering  | виняния А      |          |

|                    | EE 3302 — DIGITAL I                          | LOGIC CIRCUIT     | 'S             |          |

|                    | (Regulation                                  | s 2021)           |                |          |

| Time: Three hours  |                                              |                   | Maximum: 1     | 00 marks |

|                    | Answer ALL q                                 | questions.        |                |          |

|                    | PART A — (10 × 2                             | 2 = 20 marks)     |                |          |

| 1. What is the b   | est example of digital syst                  | tem?              |                |          |

| 2. Define Nibble   | and Byte.                                    |                   |                |          |

| 3. Define Boolea   | n algebra and Boolean Ex                     | xpression.        |                |          |

| 4. State De Mor    | gan's theorem.                               |                   |                |          |

| 5. Difference be   | tween Combinational & Se                     | equential Circuit | S.             |          |

| 6. What are the    | classifications of sequenti                  | al circuits?      |                |          |

| 7. How can the     | hazards in combinational                     | circuit be remove |                |          |

| 8. What is static  | e 1 hazard?                                  | ta S and R and a  |                |          |

| 9. What are the    | types of gate arrays in AS                   | SIC?              |                |          |

| 10. Give the diffe | rent bitwise operators.                      |                   |                |          |

|                    | PART B — (5 × 13                             | 3 = 65 marks)     | Design an as   |          |

| 11. (a) (i) Di     | aw the circuit diagram at<br>th tristate out | nd explain the w  |                | inverter |

| (ii) Ex            | xplain the concept and imp                   | olementation of I | ECL logic fami | ly.      |

|                    | Or                                           |                   |                |          |

|                    |                                              |                   |                |          |

|                    |                                              |                   |                |          |

## POLYTECHNIC, B.E/B.TECH, M.E/M.TECH, MBA, MCA & SCHOOL

Notes Syllabus Question Papers Results and Many more...

www.binils.com

Available @

- (b) (i) Explain the operation of TTL NAND gate with a neat circuit diagram. (8)

- (ii) Draw the circuit of CMOS NOR gate and explain its operation. Mention any two points about the advantages of CMOS over the other digital logic families. (5)

- 12. (a) Obtain the minimum SOP using K-map.  $F{=}M_0{+}M_2{+}M_4{+}M_8{+}M_9{+}M_{10}{+}M_{11}{+}M_{12}{+}M_{13}$

Or

- (b) Using 8:1 multiplexer, realize the Boolean function T=f(w,x,y,z)=m (0,1,2,4,5,7,8,9,12,13)

- 13. (a) A sequential circuit has four flip flops ABCD and an input x is described by the following state equations.

$$A(t+1) = (CD'+C'D)x + (CD + (CD)')x'$$

B(t+1) = A

$C\left(t+1\right)=B$

D(t+1) = C

Obtain the sequence of states when x=1 starting from state ABCD = 0001 Obtain the sequence of states when x=10 starting from state ABCD = 0000

Or

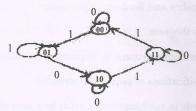

(b) Design a synchronous sequential circuit using JK for the given state diagram.

14. (a) Develop the state diagram and primitive flow table for a logic system that has two inputs S and R and a single output Q. The device is to be an edge triggered SR flip-flop but without a clock. The device changes state on the rising edges of the two inputs. Static input values are not to have any effect in changing the Q output.

Or

(b) Design an asynchronous sequential circuit that has two inputs  $X_2$  and  $X_1$  and one output Z. The output is to remain a 0 as long as  $X_1$  is a 0. The first change in  $X_2$  that occurs while  $X_1$  is a 1 will cause a Z to be a 1. Z is to remain a 1 until  $X_1$  returns to 0. Construct a state diagram and flow table. Determine the output equations.

30148

## POLYTECHNIC, B.E/B.TECH, M.E/M.TECH, MBA, MCA & SCHOOL

Notes Syllabus Question Papers Results and Many more...

www.binils.com

Available @

15. (a) Write a VHDL module that implements a full adder using an array of bit-vectors to represent the truth table.

Or

- (b) (i) Write HDL behavioral description of JK flipflop using if- else statement based on value of present state. (8)

- (ii) Draw the logic diagram for the following module. (5) module seqcrt (A,B,C,Q,CLK);

input A,B,C,CLK;

output Q: reg Q,E;

always @ (Posedge CLK) begin E<= A&B;

$Q \le E / C;$

end end module

PART C —

$$(1 \times 15 = 15 \text{ marks})$$

16. (a) An asynchronous sequential circuit has two internal states and one output. The excitation and output functions describing the circuit are

$$Y_1 = X_1 + X_1 Y_2' + X_2 Y_1 Y_2 = X_2 + X_1 Y_1' Y_2 + X_1 Y_1, Z = X_2 + Y_1$$

- (i) Draw the logic diagram of the circuit.

- (5) (5)

- (ii) Derive the transition table and output map.

- (5)

(iii) Obtain a flow table for the circuit.

Or

(b) Design an asynchronous binary toggle circuit that changes state with each rising edge of clock input. Assume the initial output as zero.

3

30148