# GOVERNMENT OF TAMILNADU DIRECTORATE OF TECHNICAL EDUCATION CHENNAI – 600 025

### STATE PROJECT COORDINATION UNIT

### **Diploma in Instrumentation and Control Engineering**

Course Code: 34241

### M – Scheme

### e-TEXTBOOK on ANALOG AND DIGITAL ELECTRONICS for IV Semester DICE

### **Convener for ICE Discipline:**

### Dr.S.Rajakumari,

Head of Department/ECE, Dr.Dharmambal Govt. Polytechnic College for Women, Tharamani, Chennai - 600 113

# Team Members for Analog And Digital Electronics:

### Tmt.Dr.S.R.Ruckmani M.E.,Ph.D.,

Lecturer (Sr.Gr.) / ICE, 210, CIT Sandwich Polytechnic College, Coimbatore – 641 014

### Mr.K.Annamalai M.E.,

Lecturer (SG) / ICE, 221, Seshasayee Institute of Technology, Tiruchirappalli – 620 010

### Tmt.D.Sivakami B.E.,

Lecturer (SG) / ICE, 280, A.D.J.Dharmambal Polytechnic College, Nagapattinam – 611 001

#### Validated By

#### Tmt.M.Muzhumathi M.E.,

Lecturer (SG) / ECE, 277, Padmabhushan Sri N Ramaswami Ayyar Memorial Polytechnic College for Girls Tiruchirappalli – 620 002

### ANALOG AND DIGITAL ELECTRONICS DETAILED SYLLABUS

| Unit | Name of the Topic                                                                                                                                                   | Pages    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | Linear ICs Op.arnps, Timers and their applications                                                                                                                  |          |

|      | Operational amplifier – Ideal Op.Amp - Block diagram and characteristics -Op-amp                                                                                    |          |

|      | parameters - CM RR - Slew rate - Virtual ground - Applications of op-amp - inverting                                                                                |          |

|      | amplifier - Summing amplifier - Non inverting amplifier - Voltage follower -                                                                                        |          |

| I    | Comparator - Zero crossing detector - Integrator - Differentiator - Op- Amp                                                                                         | 1 - 22   |

|      | Specifications.                                                                                                                                                     |          |

|      | 555 Timer - Functional Block diagram - Astable, Monostabie and Schmitt Trigger -                                                                                    |          |

|      | Sequence timer,555 timer can be used as PWM.                                                                                                                        |          |

|      | Boolean Algebra                                                                                                                                                     |          |

|      | Number systems - Decimal - Binary - Octal - Hexadecimal - BCD - Conversion                                                                                          |          |

|      | from one number system to other - Boolean Algebra -Basic laws and Demargan's                                                                                        |          |

|      | Theorems - Logic gates - OR - AND - NOT - NOR - NAND - EX-OR Symbols, Truth                                                                                         |          |

| П    | table and Boolean expression - Realization of gates using universal gates                                                                                           | 23 - 45  |

|      | NAND. and NOR - Problems using 2, 3, and 4 variables - Boolean expression                                                                                           | 23 43    |

|      | for outputs - Simplification of Boolean expression using Kamaugh map (up to 4                                                                                       |          |

|      | variable)- Constructing logic circuits for the Boolean expressions                                                                                                  |          |

|      |                                                                                                                                                                     |          |

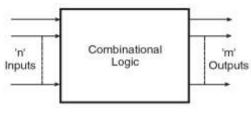

|      | Combinational Logic                                                                                                                                                 |          |

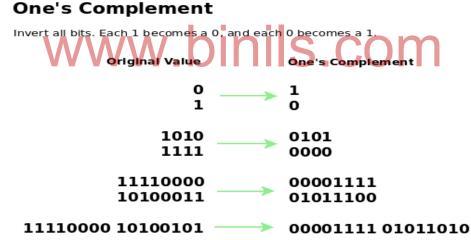

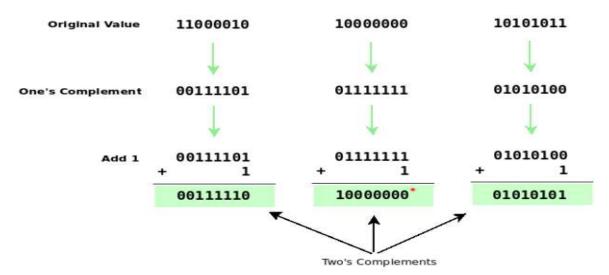

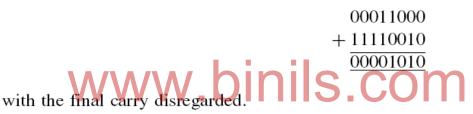

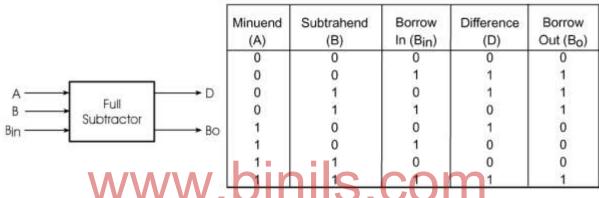

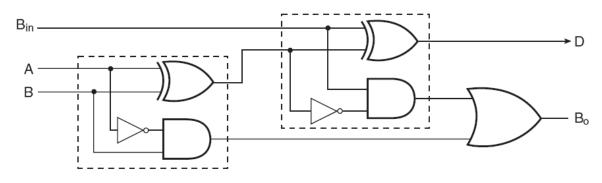

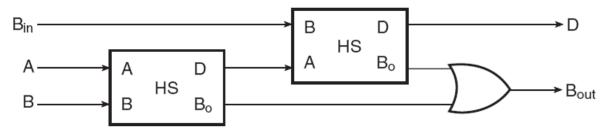

|      | Arithmetic circuits - Binary addition – Binary Subtraction - I's complement and 2's                                                                                 |          |

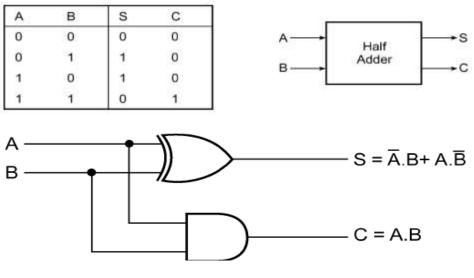

|      | complement - Signed binary numbers - Half adder - Full adder - Half subtractor -                                                                                    |          |

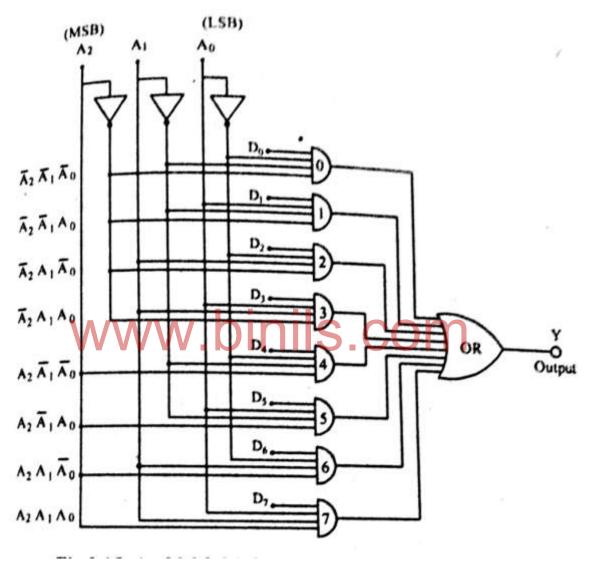

| ш    | Full subtractor - Parity Generator and checker - Digital comparator - Arithmetic<br>Logic Unit - Decoder - 3 to 8 decoder - BCD to seven segment decoder -Encoder - | 46 - 70  |

|      | Multiplexer - Demuitiplexer - Digital Logic families - TTL - CBIOS - LS series - Fan                                                                                |          |

|      | in - Fan out - Propagation delay -Noise immunity for the above families.                                                                                            |          |

|      | Sequential Logic                                                                                                                                                    |          |

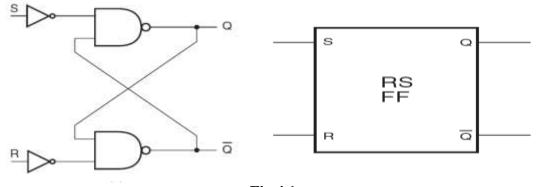

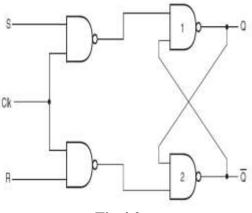

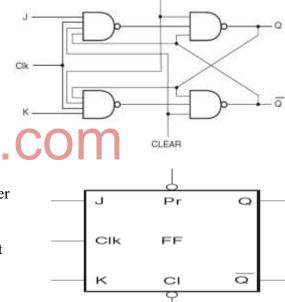

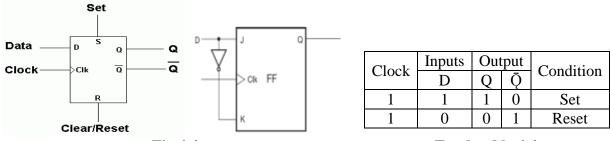

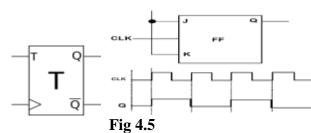

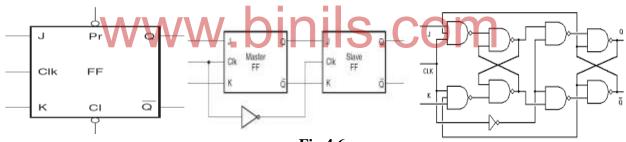

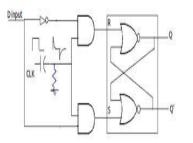

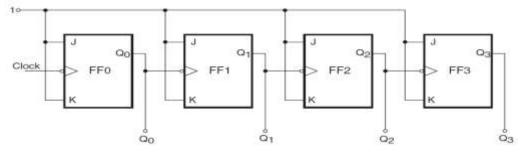

|      | Flip-flops - RS - 0 - T - JK - Master Slave Flip Flops - Edge triggered FE -                                                                                        |          |

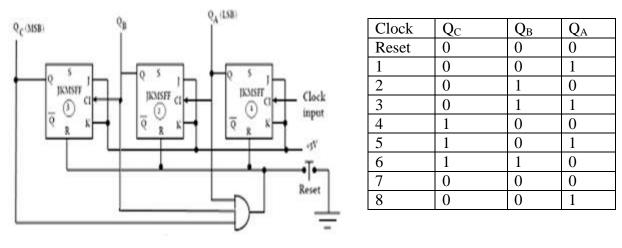

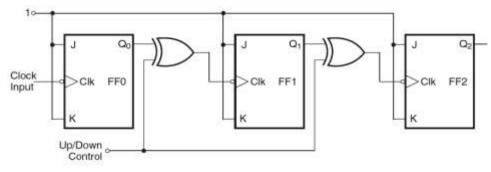

|      | Asynchronous Binary Counter - Decade counter - Mod n counter - Up Down                                                                                              |          |

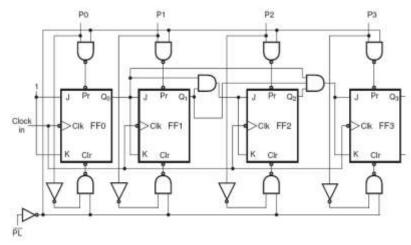

| IV   | Counter - Preset table counter - Ring counter - Johnson counter -                                                                                                   | 71 - 93  |

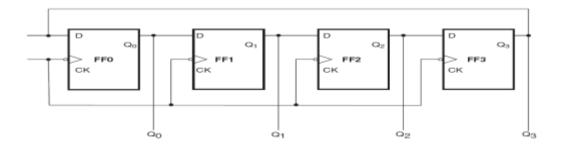

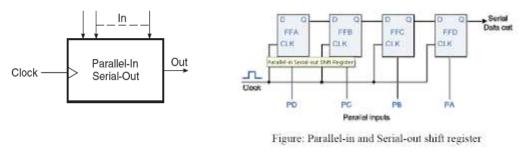

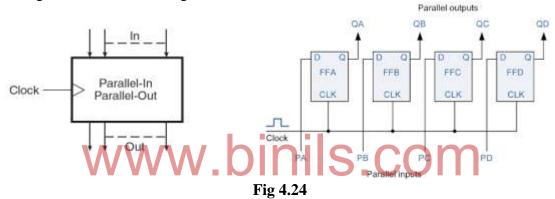

|      | Synchronous counter - State diagram - Shift register - 4 bit shift register -                                                                                       |          |

|      | Serial in Serial out - Serial in Parallel out - Parallel in serial out                                                                                              |          |

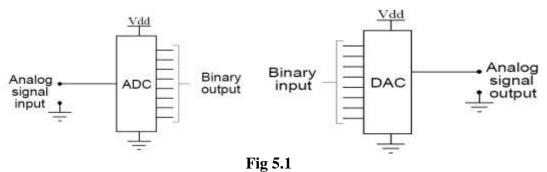

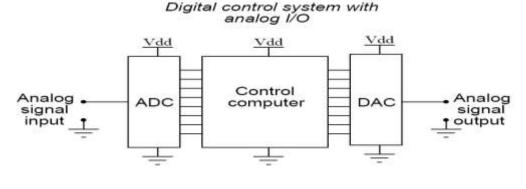

|      | DIA, AID and Memory                                                                                                                                                 |          |

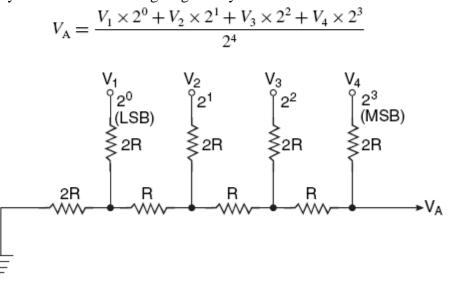

|      | DIA Converter - Basic concepts - Weighted Resistor D/A converter - R-2R                                                                                             |          |

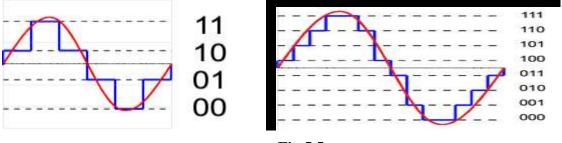

|      | Ladder DIA converter - Specification of DAC IC. Sampling and quantization -                                                                                         |          |

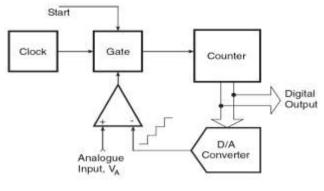

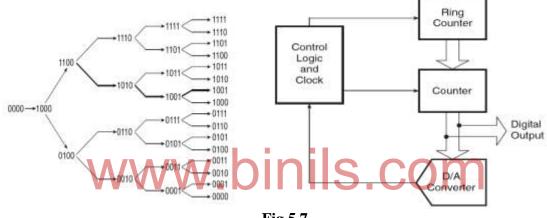

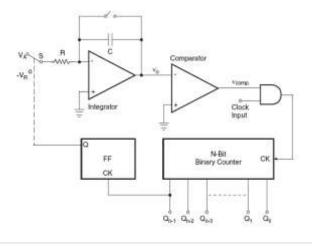

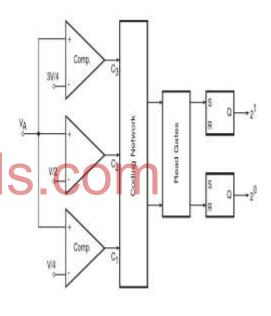

|      | Analog to digital conversion using Ramp method - Successive                                                                                                         |          |

| v    | approximation method - Dual slope method. simultaneous method                                                                                                       | 94 - 109 |

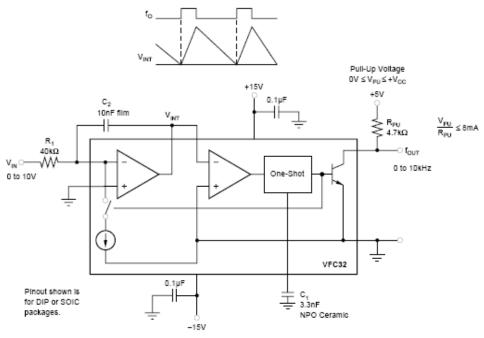

|      | voltage to frequency converter - Frequency to voltage converter specification of ND                                                                                 |          |

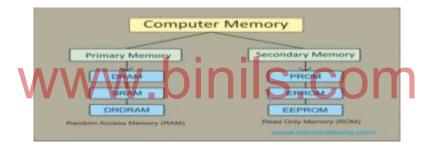

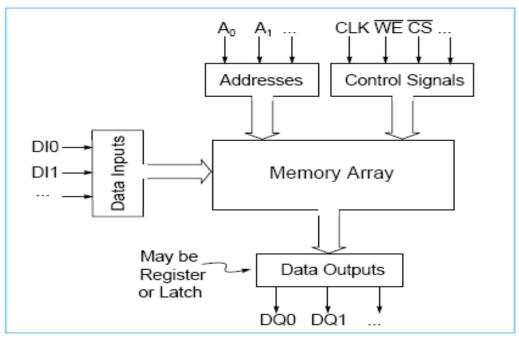

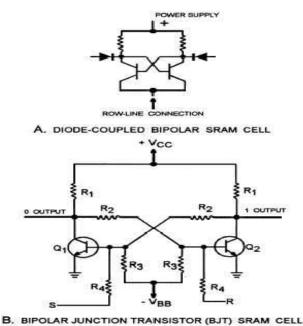

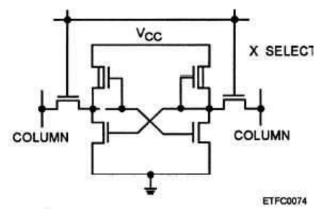

|      | converter Memory - Static Memory - Dynamic Memory - Static Memory                                                                                                   |          |

|      | organization in terms of address lines, control lines and data lines —                                                                                              |          |

|      |                                                                                                                                                                     |          |

### LINEAR ICS: OP-AMPS, TIMERS AND THEIR APPLICATIONS 1.1 The operational amplifier:

An operational amplifier is a direct coupled high gain amplifier consisting of one or more differential (OPAMP) amplifiers and followed by a level translator and an output stage. An operational amplifier is available as a simplex integrated circuit package.

An operational amplifier is designed to perform mathematical operations like addition, subtraction, differentiation, integration, multiplication, division etc in analog computers. Hence it is called as operational amplifiers.

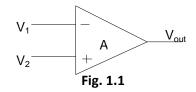

### **Symbol of Operational Amplifier:**

1. In fig 1.1 an op.amp contains two inputs and a single output. The inputs are named as inverting

input marked with a negative or "minus" sign, (-) and non-inverting input marked with a

positive or "plus" sign (+).

- 2. If the non-inverting input is grounded and a signal is applied to the inverting input, the

- output signal will be 180 degrees out of phase with the input signal.

- 3. If the inverting input is grounded and a signal is applied to the non-inverting input, the

output signal will be in phase with the input signal.

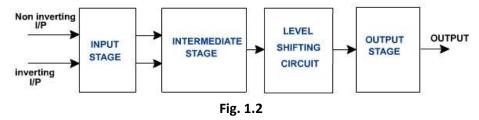

### **Block Diagram of Op-Amp**

The block diagram of Op-Amp is shown in Fig. 1.2.

The input stage is a dual input balanced output differential amplifier. This stage provides most of the voltage gain of the amplifier and also establishes the input resistance of the Op-Amp. The intermediate stage of Op-Amp is another differential amplifier which is driven by the output of the first stage. This is usually dual input unbalanced output.

Because of direct coupling, the dc voltage level at the output of intermediate stage is well above ground potential. Therefore level shifting circuit is used to shift the dc level at the output downwards to zero with respect to ground. The output stage is generally a push pull complementary amplifier. The output stage increases the output voltage swing and raises the current supplying capability of the Op-Amp. It also provides low output resistance.

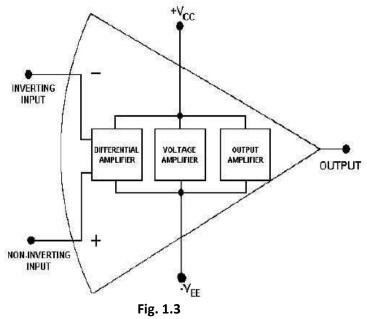

### AN IDEAL OP.AMP:

An ideal op.amp shown in Fig. 1.3 is a differential input and a single ended output device.

### CHARACTERISTICS OF AN IDEAL OP.AMP.

- 1. High input impedance  $R_i = \infty$

- 2. Low output impedance  $R_0 = 0$

- 3. Infinite open loop gain  $A_v = \infty$

- 4. Infinite bandwidth  $BW = \infty$

5. Perfect balance  $V_0 = 0$  when  $V_1 = V_2$ Characteristics do not change with temperature.

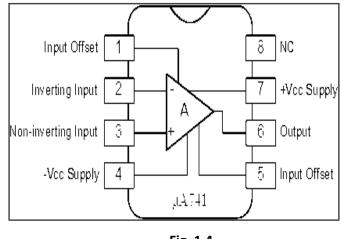

### PIN DIAGRAM OF AN OP.AMP

Operational amplifiers are available in IC packages of either single, dual or quad opamps within one single chip. The most commonly available operational amplifiers in basic electronic kits and projects is the industry standard µA-741 IC show in Fig. 1.4

Fig. 1.4

### Parameters of OP AMP (Specifications):

| Sl. No. | Parameters                         |

|---------|------------------------------------|

| SI. NO. |                                    |

| 1       | Input offset Voltage               |

| 2       | Input offset current               |

| 3       | Input Bias Current                 |

| 4       | Large Signal Voltage gain          |

| 5       | Output Voltage Swing               |

| 6       | Differential input resistance Ri   |

| 7       | Input Capacitance Ci               |

| 8       | Common Mode Rejection Ratio(CMRR)  |

| 9       | Supply voltage Rejection Ratio     |

| 10      | Slew Rate                          |

| 11      | Gain Bandwidth Product             |

| 12      | Maximum differential input voltage |

| 13      | Maximum common mode input voltage  |

### 1)Input offset Voltage

Input offset voltage is the voltage that must be applied between the two input terminals of an op-amp to null the output.

### 2) Input offset current

The algebraic difference between the current in the inverting and non inverting terminal is known as the input offset current

### 3) Input Bias Current

IB is the average current flows in the inverting and non-inverting terminal of an opamp.

IB = (IB1 + IB2)/2

### 4) Large Signal Voltage gain

It is the ratio of the output voltage and the differential input voltage

A = Outputvoltage/Differential input voltage = Vo/Vid

### 5) Output Voltage Swing

This parameter indicates the values of positive and negative saturation voltage of the op-amp. For 741 IC, it is +13 and -13V.

### 6) Differential input resistance Ri

Differential input resistance Ri is the equivalent resistance that can be measured at either the inverting or non-inverting input terminals with the other terminal connected to ground.

Typical value for 741 IC is 2 mega ohm.

### 7) Input Capacitance Ci

Input capacitance is the equivalent capacitance that can be measured at either the inverting or non-inverting input terminal with the other terminal connected to ground.

Typical value for a 741 IC is 1.4 pF.

### 8) Common Mode Rejection Ratio(CMRR)

When the same voltage is applied to both the input terminals the voltage is called a common mode voltage(Vcm) and the op-amp is said to be operating in the common mode configuration, CMRR is defined as the ratio of the differential mode voltage gain ( $A_d$ ) and common mode voltage gain.

CMRR = Ad/Acm

### 9) Supply voltage Rejection Ratio

The change in an op-amps input offset voltage Vio caused by variations in the supply voltage is called the SVRR. It is expressed in microvolts per volt or in decibels.

$SR = \Delta Vio/\Delta V$

### 10) Slew Rate

Slew rate is defined as the maximum rate of change of output voltage per unit of time and is expressed as volts per micro second.

### **11) Gain Bandwidth Product**

The gain bandwidth product (GB) is the bandwidth of the op-amp when the voltage gain is 1. Typical value for 741 IC is 1MHz.

### 12) Maximum differential input voltage

It is the maximum value of differential input voltage that can be applied without damaging the op-amp.

### **13) Maximum common mode input voltage**

It is the maximum voltage to which that the two inputs can be raised above ground potential before the op-amp becomes non-linear

### VIRTUAL GROUND

In op-amp, the differential input voltage is ideally zero, that is the voltage at the inverting terminal  $V_1$  is approximately equal to that at the non inverting terminal  $V_2$  In other words, the inverting terminal voltage  $V_1$  is approximately at ground potential. The inverting terminal is not directly connected to ground. But it acts like a ground terminal. Therefore the inverting terminal is said to be at virtual ground

### **ADVANTAGES OF OP-AMP**

- i) Inexpensive

- ii) Versatile

- Easy to use

# iii) Easy to use <u>APPLICATIONS OF OP-AMP</u> i) Used in negative amplifiers

- i) Used in negative amplifiers.

- ii) Used in wave shaping circuits

- iii) Used in filter circuit

- iv) Used in many mathematical operations.

- v) Used as inverting amplifier

- vi) Used as an non-inverting amplifier

- vii)Other applications includes

- (a) summing amplifier

- (b) multiplier or scale changer

- (c) integrator

- (d) differentiator

- (e) Voltage follower.

- (f) Comparator

- (g) Zero crossing detector, etc

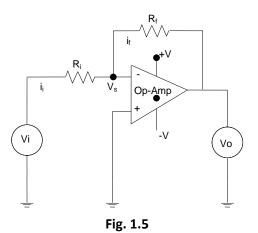

### **1.2 INVERTING AMPLIFIER:**

If an input is applied to the inverting terminal, the output is 180 out of phase with the input signal. Hence it is called as INVERTING AMPLIFIER.

The Fig. 1.5 shows an inverting amplifier using op amp. Input is applied to the inverting terminal through R<sub>in</sub>. Non-inverting terminal is grounded. A suitable resistor R<sub>F</sub> is connected across the amplifier from the output terminal back to the inverting input terminal This negative feedback is used to reduce and control the overall gain of the amplifier. The junction of the input and feedback signal (X) is at the same potential as the

4 | Page

positive (+) input which is at zero volts or ground then, the junction is said to be in **"Virtual ground."**

**Due to its virtual ground,** No Current Flows into the Input Terminals and the Differential Input Voltage is Zero as V1 = V2 = 0.Hence, the current flowing through the input resister  $R_{in}$  is equal to the current flowing through the feedback resistor  $R_F$  Applying Kirchoff's voltage law,

$$i_{n} = i_{f}$$

$$\frac{V_{i} - V_{s}}{R_{i}} = \frac{V_{s} - V_{0}}{R_{f}}$$

Substitute  $V_{s} = 0$  due to virtual ground

$$\frac{V_{i} - 0}{R_{i}} = \frac{0 - V_{0}}{R_{f}}$$

$$\frac{V_{i}}{R_{i}} = \frac{-V_{0}}{R_{f}}$$

$$\frac{R_{f}}{R} v_{i} = -v_{o} \text{ biniss.com}$$

$$\begin{bmatrix} \frac{R_{f}}{R}}{R} v_{i} = -V_{o} \end{bmatrix}$$

Then, the Closed-Loop Voltage Gain of an Inverting Amplifier is given as.

Gain (Av) =

$$\frac{V_{out}}{V_{in}} = -\frac{R_f}{R_{in}}$$

and therefore Vout is

$$Vout = -\frac{Rf}{Rin} \times Vin$$

From the above equation, the output voltage of an inverting amplifier is equal to the input voltage multiplied with gain. The minus sign indicates input is given to inverting terminal.

If  $RF = R_{IN} = R$ , V out = -Vin

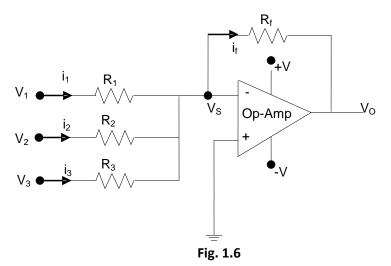

### **1.3 The Summing Amplifier:**

As its name suggests, the output of the "summing amplifier" is the sum of input voltages in reverse direction. It is also called as *summing inverter*" or a "voltage adder".

The above circuit shows in fig 1.6 the summing amplifier using op amp. In this circuit, the output voltage, (Vout) proportional to the sum of the input voltages, V1, V2, V3etc.

According to Kirchoff's current law, the sum of the current flowing through input resistors is equal to the current flowing through feedback resister.

$$i_{n} = i_{f}$$

$$i_{n} = i_{1} + i_{2} + i_{3} = i_{f}$$

$$\frac{V_{1} - V_{s}}{R_{1}} + \frac{V_{2} - V_{s}}{R_{2}} + \frac{V_{3} - V_{s}}{R_{3}} = \frac{V_{s} - V_{0}}{R_{f}}$$

Substitute  $V_s$ = 0 due to virtual ground

$$\frac{V_{1}-0}{R_{1}} + \frac{V_{2}-0}{R_{2}} + \frac{V_{3}-0}{R_{3}} = \frac{0-V_{0}}{R_{f}}$$

$$\frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{3}} = -\frac{V_{0}}{R_{f}}$$

If  $R_{1} = R_{2} = R_{3} = R$ ,

$\frac{V_{1}}{R} + \frac{V_{2}}{R} + \frac{V_{3}}{R} = -\frac{V_{0}}{R_{f}}$

$\frac{1}{R} (V_{1} + V_{2} + V_{3}) = -\frac{V_{0}}{R_{f}}$

$-\frac{R_{f}}{R} (V_{1} + V_{2} + V_{3}) = V_{0}$

If  $R_{f} = R$ ,

$V_{0} = -(V_{1} + V_{2} + V_{3}) \times \frac{R}{R}$

$V_{0} = -(V_{1} + V_{2} + V_{3})$

**From the above equation, the output voltage is equal to the sum of the input voltages.** The minus sign indicates input is given to inverting terminal.

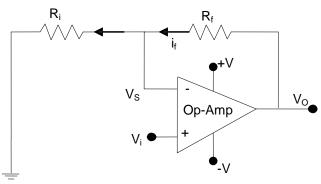

### **1.4 The Non-inverting Operational Amplifier**

If an input is applied to the non-inverting terminal ,the output in phase with the input signal.Hence it is called as NON- INVERTING AMPLIFIER.So, the output gain of the amplifier becomes "Positive" in value in contrast to the "Inverting Amplifier" circuit The above figure shows a non-inverting amplifier using op amp. Input is directly

6 | Page

applied to the non- inverting terminal. Inverting terminal is grounded through the resistor  $R_{2.}$  A suitable resistor

Fig. 1.7

$R_F$  is connected across the amplifier from the output terminal back to the inverting input terminal .This negative feedback is used to **reduce and control the overall gain of the amplifier**

The above fig 1.7 shows a non- invertin amplifier using op amp. Input is directly applied to the non- inverting terminal. Inverting terminal is grounded through the resistor  $\mathbf{R}_{i}$ . A suitable resistor  $\mathbf{R}_{F}$  is connected across the amplifier from the output terminal back to the inverting input terminal .This negative feedback is used to reduce and control the overall gain of the amplifier.

Applying kirchoff's current law at the inverting terminal,

$$I_{i} = I_{f}$$

$$\frac{V_{s}}{R_{i}} = \frac{V_{0} - V_{s}}{R_{f}}$$

Substitute  $V_{s} = V_{i}$  in the flue above equation, **S** COM

$$\frac{V_{i}}{R_{i}} = \frac{V_{0} - V_{i}}{R_{f}}$$

$$\frac{V_{i}}{R_{i}} = \frac{V_{0}}{R_{f}} - \frac{V_{i}}{R_{f}}$$

$$\frac{V_{0}}{R_{f}} - \frac{V_{i}}{R_{f}} = \frac{V_{i}}{R_{i}}$$

$$\frac{V_{0}}{R_{f}} = \frac{V_{i}}{R_{i}} + \frac{V_{i}}{R_{f}}$$

$$\frac{V_{0}}{R_{f}} = V_{i} \left(\frac{1}{R_{i}} + \frac{1}{R_{f}}\right)$$

$$V_{0} = V_{i} R_{f} \left(\frac{1}{R_{i}} + \frac{1}{R_{f}}\right)$$

$$V_{0} = V_{i} \left(\frac{R_{f}}{R_{i}} + \frac{R_{f}}{R_{f}}\right)$$

$$V_{0} = V_{i} \left(\frac{R_{f}}{R_{i}} + \frac{R_{f}}{R_{f}}\right)$$

$$V_{0} = V_{i} \left(\frac{R_{f}}{R_{i}} + 1\right)$$

Then the closed loop voltage gain of a Non-inverting Operational Amplifier will be given as

$$\frac{V_o}{V_i} = \left(1 + \frac{R_f}{R_i}\right)$$

$$A_V = \frac{V_o}{V_i} = \left(1 + \frac{R_f}{R_i}\right)$$

### **7 |** Page

From the above equation, the overall closed-loop gain of a non-inverting amplifier will always be greater but never less than one (unity), it is positive in nature and is determined by the ratio of the values of Rf and Ri.

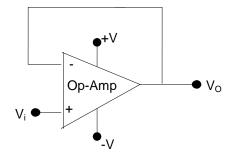

### **1.5 Voltage Follower:**

Voltage follower is an example of non-inverting amplifier. The output of the voltage follower follows the input voltage. Hence, it is called as unity gain amplifier.

Fig. 1.8

In fig 1.8 Input is applied to the non-inverting terminal. Output is directly fed back to the inverting terminal without any feedback component.

The output of a non-inverting amplifier is given as

$$V_0 = \left(1 + \frac{R_f}{R_i}\right) V_i$$

If  $R_f = 0 \& R_i = \infty$ ,

the output voltage  $V_0$  becomes

$$V_0 = \left(1 + \frac{0}{\infty}\right) V_i$$

$$V_0 = V_i$$

$$V_0 = V_i$$

From the above equation, the output voltage  $V_0$  follows the input voltage  $V_i$ . Hence it is called as voltage follower

$$\operatorname{Gain} A_V = \frac{V_0}{V_i} = 1$$

Hence, The gain of the voltage follower is unity. It is otherwise called as unity gain amplifier.

**Applications:** 1.

1. used for impedance matching.

2. used as buffer.

3. used as unity gain amplifier.

### **1.6 COMPARATOR**

8 | Page www.binils.com Anna University, Polytechnic & Schools

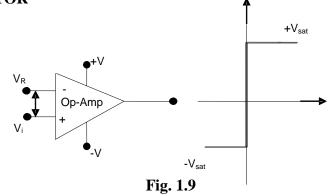

Comparator compares two voltages of fixed reference voltage  $V_R$  and an analog input voltage  $V_i$ .

Input voltage  $V_i$  is applied to the non-inverting terminal and reference voltage  $V_R$  is applied to the inverting terminal shown in fig 1.9 If input voltage  $V_i$  is greater than  $V_{Ref}$ , the output of the op amp goes to positive saturation level.

If input voltage  $V_i$  is less than  $V_{Ref}$ , the output of the op amp goes to negative saturation level.

If the input voltage is equal to  $V_{Ref}$ , the output is equal to zero.

It is given as

i) if

$$V_i > V_{Ref}$$

,  $V_0 = + V_{sat}$

ii) if

$$V_i > V_{Ref}$$

,  $V_0 = -V_{sat}$

iii) if

$$V_i = V_{Ref}, V_0 = 0$$

**Application:**

Used as sine wave to square wave generators

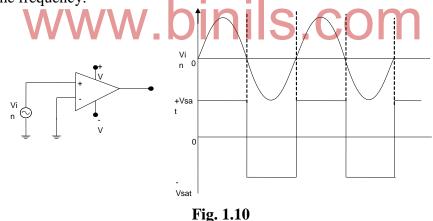

### **1.7 SINE WAVE TO SQUARE WAVE GENERATOR:**

It is one of the applications of comparator. In fig1.10 Input is applied to the noninverting input of op.amp. The inverting terminal of op.amp is grounded. So, the voltage at the inverting input is zero.

During the positive half cycle, the voltage at the non-inverting terminal is greater than the voltage at the inverting terminal. So, the output goes to positive saturation+ $V_{sat}$ .

During the negative half cycle, the voltage at the non-inverting terminal is less than the voltage at the inverting terminal. So, the output goes to negative saturation  $-V_{sat}$ .

Thus, a sine wave at the input of op amp is converted into square wave without changing the frequency.

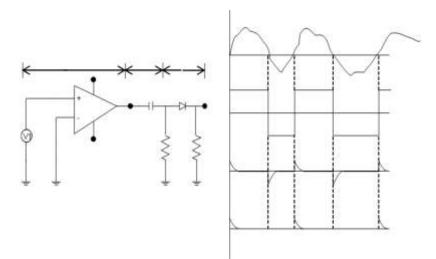

#### **1.8 ZERO CROSSING DETECTOR:**

Zero crossing detectors are a circuit whose output changes from one state to another state when the input signal passes through zero.

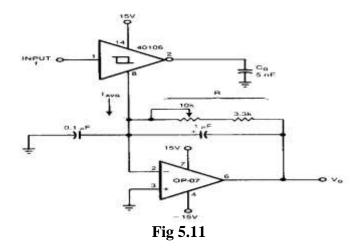

Pn fig 1.11 It consists of comparator, differentiator and half wave rectifier. The comparator produces rectangular signal with respect to the input signal. Then the differentiator produces positive and negative spike according to the differentiator input. The diode D rectifies and produces positive pulse only. (i.e.) when the input signal crosses from negative to positive voltage through zero, positive pulses are produced at its output. It is an another application of comparator. If the inverting terminal of comparator is grounded, it act as zero crossing detector.

Fig. 1.11

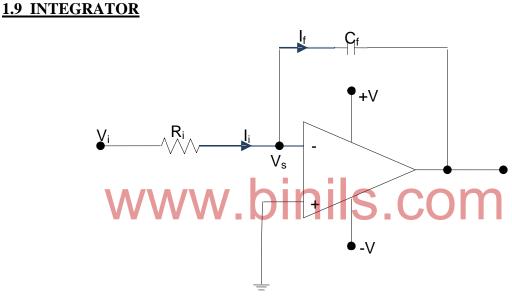

Fig. 1.12

An integrator is a circuit shown in fig 1.12 whose output voltage is proportional to the integral of the input voltage. Input  $V_i$  is applied to the inverting terminal through  $R_i$  and feedback is applied through capacitor  $C_f$ . The non-inverting terminal is grounded. When input voltage is applied, the charge in the capacitor  $C_f$  is given as

$$Q = CV$$

We know that current through the capacitor

$$I_{C} = \frac{dQ}{dt}$$

where Q =CV

$$\therefore I_{C} = \frac{dcv}{dt}$$

$$I_{C} = C\left(\frac{dv}{dt}\right)$$

## **10 |** Page

where c is constant

Applying KCL,

$$i_i = i_f$$

$$\frac{V_i - V_s}{R_i} = C_f \frac{dv}{dt}$$

where  $V = V_s - V_0$

$$\frac{V_i - V_s}{R_i} = C_f \frac{d(V_s - V_0)}{dt}$$

Due to virtual ground  $V_S = 0$

$$\frac{V_i - 0}{R_i} = C_f \frac{d(0 - V_0)}{dt}$$

$$\frac{V_i}{R_i} = -C_f \frac{dV_0}{dt}$$

$$C_f \frac{dV_0}{dt} = -\frac{V_i}{R_i}$$

$$\frac{dV_0}{dt} = -\frac{V_i}{R_i}$$

Integrate on both sides, we get

WWW

$$\int \frac{dV_0}{dt} + \Pi \int \frac{V_t}{R_t C_f} \cdot COM$$

$$V_0 = -\frac{1}{R_i C_f} \int V_i dt$$

From the above equation, the output voltage is equal to the integral of input voltage in reverse direction.

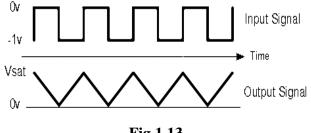

If a square wave input is applied to the integrator, it will produce triangular output show in fig 1.13

**Fig 1.13**

### **1.10 DIFFERENTIATOR:**

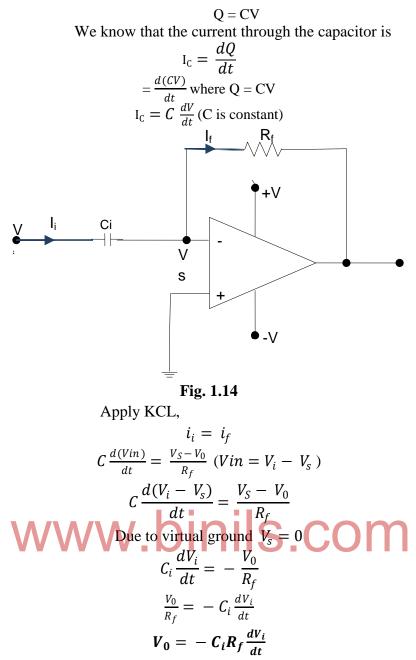

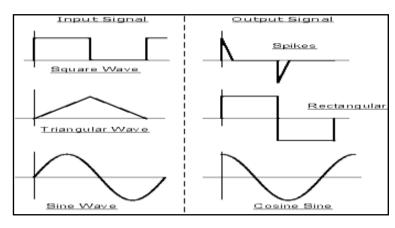

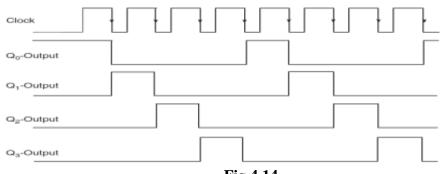

Differentiator is a circuit whose output is directly proportional to the derivative of the input in reverse direction. Shown fig 1.14 Input is applied to the inverting terminal through C<sub>i</sub> and feedback is applied through R<sub>f.</sub> The non-inverting terminal is grounded. When an input voltage V<sub>i</sub> is applied, the charge on the capacitor is

**11** | Page

From the above equation the output voltage is equal to the derivative of the input voltage in reverse direction (with respect to time). If a square wave input is applied to the differentiator, it will produce a spike output shown fig 1.15

### 1.11 Timer IC.

### **Introduction 555 timer IC**

The 555 timer IC was introduced in the year 1970 by Signetic Corporation and gave the name **SE/NE 555 timer**. It is basically a monolithic timing circuit that produces accurate and highly stable time delays or oscillation. When compared to the applications of an op-amp in the same areas, **the 555IC is also equally reliable and is cheap in cost**. Its applications are

monostable multivibrator and astable multivibrator,

dc-dc converters

digital logic probes,

waveform generators,

analog frequency meters

and tachometers, temperature measurement

and control devices, voltage regulators etc.

The timer IC is setup to work in either of the two modes – one-shot or monostable or as a free-running or astable multivibrator. The **SE 555** can be used for temperature ranges between  $-55^{\circ}$ C to  $125^{\circ}$ . The **NE 555** can be used for a temperature range between  $0^{\circ}$ to  $70^{\circ}$ C. **The important features of the 555 timer are:**

- 1.It operates from a wide range of **power supplies** ranging from +5 Volts to +18 Volts supply voltage.

- 2.Sinking or sourcing 200 mA of load current.

- 3. The output of a 555 timer can drive transistor-transistor logic (TTL) due to its high current output.

- 4.It has a temperature stability of 50 parts per million (ppm) per degree Celsius change in temperature, or equivalently 0.005 % / °C.

- 5. The duty cycle of the timer is adjustable

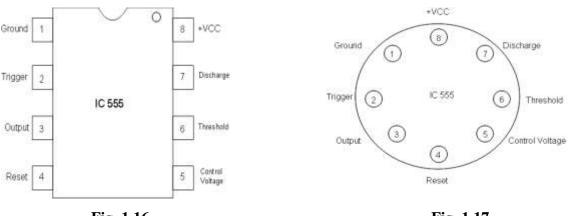

### IC Pin Configuration

Fig. 1.16

Fig. 1.17

The 555 Timer IC is available as an 8-pin metal can, an 8-pin mini DIP (dual-in-package) or a 14-pin DIP. The pin configuration is shown in the figures. 1. 16 and 1.17

This IC consists of 23 transistors, 2 diodes and 16 <u>resistors</u>. The use of each pin in the IC is explained below. The pin numbers used below refers to the 8-pin DIP and 8-pin metal

can packages. These pins are explained in detail, and you will get a better idea after going through the entire post

Fig. 1.18

### **Block Diagram**

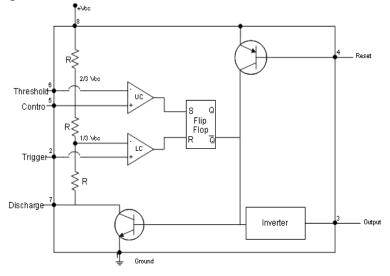

In fig 1.18 A 555 timer has two comparators, an R-S flip-flop, two transistors and a resistive network.

- Resistive network consists of three equal resistors and acts as a voltage divider.

- Comparator 1 compares threshold voltage with a reference voltage  $+ 2/3 V_{CC}$  volts.

- Comparator 2 compares the trigger voltage with a reference voltage + 1/3 V<sub>CC</sub> volts.

Output of both the comparators is supplied to the flip-flop. Flip-flop assumes its state according to the output of the two comparators. One of the two transistors is a discharge transistor of which collector is connected to **pin** 7. This transistor saturates or cuts-off according to the output state of the flip-flop. The saturated transistor provides a discharge path to a capacitor connected externally. Base of another transistor is connected to a reset terminal. A pulse applied to this terminal resets the whole timer irrespective of any input

### **Working Principle**

- 1. The internal resistors act as a voltage divider network, providing (2/3)Vcc at the non-inverting terminal of the upper comparator and (1/3)Vcc at the inverting terminal of the lower comparator.

- 2. Upper comparator has a threshold input (pin 6) and a control input (pin 5).

- 3. Output of the upper comparator is applied to set (S) input of the flip-flop.

- 4. Whenever the threshold voltage exceeds the control voltage, the upper comparator will set the flip-flop and its output is high.

- 5. *A* high output from the flip-flop when given to the base of the discharge transistor saturates it and thus discharges the transistor that is connected externally to the discharge pin 7.

- 6. The complementary signal out of the flip-flop goes to pin 3, the output. The output available at pin 3 is low. These conditions will prevail until lower comparator triggers the flip-flop.

### **14 |** Page

- 7. Even if the voltage at the threshold input falls below (2/3) V<sub>CC</sub>, that is upper comparator cannot cause the flip-flop to change again. It means that the upper comparator can only force the flip-flop's output high.

- 8. To change the output of flip-flop to low, the voltage at the trigger input must fall below + (1/3) Vcc. When this occurs, lower comparator triggers the flip-flop, forcing its output low.

### **Different Modes of Operation**

Generally, the 555 timer can be operated in three modes: Astable, Monostable (or one-shot). **Astable Mode**

In this mode, the 555 work as a **free running mode**. The output of astable multivibrator will continuously toggle between low and high, there by generating a train of pulse,

### **Monostable Mode**

In the monostable mode, as the name suggests, it stays in its stable state until and unless an external trigger is applied. In this mode, the 555 functions as a "one-shot" pulse generator.

### Features

Some of the important features of the 555 timer are

- The 555 timer can be operated at a wide range of power supplies ranging from 5V to 18V.

- It is available in 3 different packages: 8-pin Metal Can package, 8-pin DIP and 14-pin DIP.

- Timing can be anywhere from microseconds to hours.

- It can operate in both astable and monostable modes.

- High output current.

- It has an adjustable duty cycle.

- It is TTL compatible due to its high output current.

- The output can source or sink a current OmA to the load.

It has a temperature stability of 0.005% per OC

### **<u>1.11.1 Astable Mode</u>**

### **Circuit and Operation**

Astable multivibrator is also called as Free Running Multivibrator. It has no stable states and continuously switches between the two states without application of any external trigger.

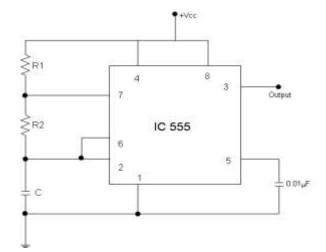

The IC 555 can be made to work as an astable multivibrator with the addition of three external components: two resistors (R1 and R2) and a capacitor (C). The schematic of the IC 555 as an astable multivibrator along with the three external components is shown fig 1.19.

Fig. 1.19

The pins 2 and 6 are connected and hence there is no need for an external trigger pulse. It will self trigger and act as a **free running multivibrator**.

The rest of the connections are as follows: pin 8 is connected to supply voltage (VCC). Pin 3 is the output terminal and hence the output is available at this pin. Pin 4 is the external reset pin. A momentary low on this pin will reset the timer. Hence when not in use, pin 4 is usually tied to VCC

The control voltage applied at pin 5 will change the threshold voltage level. But for normal use, pin 5 is connected to ground via a capacitor (usually  $0.01 \mu$ F).

### **Operation**

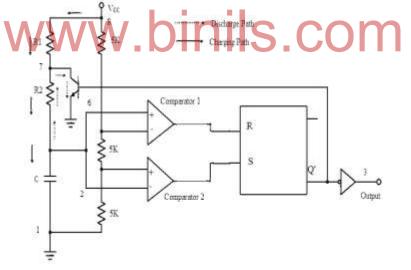

The following depicts the fig 1.20 e internal circuit of the IC 555 operating in astable mode. The RC timing circuit incorporates R1, R2 and C.

Fig. 1.20

- 1. Initially, on power-up, the flip-flop is RESET (and hence the output of the timer is low). As a result, the discharge transistor is driven to saturation (as it is connected to Q').

- 2. The capacitor C of the timing circuit is connected at Pin 7 of the IC 555 and will discharge through the transistor.

- 3. The output of the timer at this point is low. The voltage across the capacitor is nothing but the trigger voltage.

- 4. So while discharging, if the capacitor voltage becomes less than 1/3 VCC, which is the reference voltage to trigger comparator (comparator 2), the output of the comparator 2

will become high. This will SET the flip-flop and hence the output of the timer at pin 3 goes to HIGH.

- 5. This high output will turn OFF the transistor.

- 6. As a result, the capacitor C starts charging through the resistors R1 and R2. Now, the capacitor voltage is same as the threshold .

- 7. While charging, the capacitor voltage increases exponentially towards VCC and the moment it crosses 2/3 VCC, which is the reference voltage to threshold comparator (comparator 1), its output becomes high.

- 8. As a result, the flip-flop is RESET. The output of the timer falls to LOW. This low output will once again turn on the transistor

- 9. which provides a discharge path to the capacitor. Hence the capacitor C will discharge through the resistor R2. And hence the cycle continues.

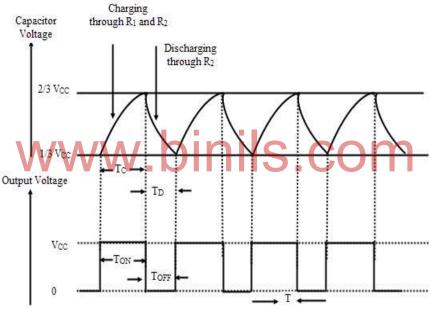

Thus, when the capacitor is charging, the voltage across the capacitor rises exponentially and the output voltage at pin 3 is high. Similarly, when the capacitor is discharging, the voltage across the capacitor falls exponentially and the output voltage at pin 3 is low. The shape of the output waveform is a train of rectangular pulses. Shown fig 1.21

Fig. 1.21

While charging, the capacitor charges through the resistors R1 and R2. Therefore the charging time constant is (R1 + R2) C as the total resistance in the charging path is R1 + R2. While discharging, the capacitor discharges through the resistor R2 only. Hence the discharge time constant is R2C

### **Duty Cycle**

The charging and discharging time constants depends on the values of the resistors R1 and R2. Generally, the charging time constant is more than the discharging time constant. Hence the HIGH output remains longer than the LOW output and therefore the output waveform is not symmetric. Duty cycle is the mathematical parameter that forms a relation between the high output and the low output.

Duty Cycle is defined as the ratio of time of HIGH output i.e. the ON time to the total time of a cycle.

**17 |** Page

If TON is the time for high output and T is the time period of one cycle, then the duty cycle D is given by

$D = T_{ON} / T$

Therefore, percentage Duty Cycle is given by

$$%D = (T_{ON} / T) * 100$$

T is sum of  $T_{ON}$  (charge time) and  $T_{OFF}$  (discharge time).

The value of  $T_{ON}$  or the charge time (for high output)  $T_C$  is given by

$T_C = 0.693 * (R1 + R2) C$

The value of  $T_{OFF}$  or the discharge time (for low output)  $T_D$  is given by

$T_D = 0.693 * R2C$

Therefore, the time period for one cycle T is given by

$$T = T_{ON} + T_{OFF} = T_C + T_D$$

$$T = 0.693 * (R1 + R2) C + 0.693 * R2C$$

$$T = 0.693 * (R1 + 2R2) C$$

Therefore, %D = (T<sub>ON</sub>/T) \* 100

D = (0.693 \* (R1 + R2) C)/(0.693 \* (R1 + 2R2) C) \* 100D = ((R1 + 2R2))/((R1 + 2R2)) \* 100

If T = 0.693 \* (R1 + R2) C, then the frequency f is given by

f = 1 / T = 1 / 0.693 \* (R1 + 2R2) C

f = 1.44/((R1 + 2R2)C)Hz

### 1.11.2 Circuit of 555 timer as Schmitt Trigger

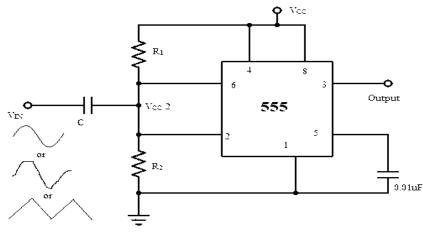

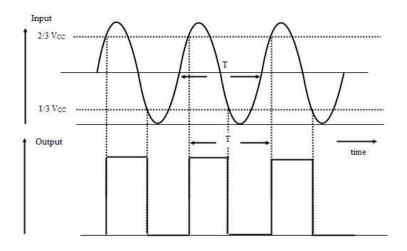

**T**he following circuit shows fig 1.22 the structure of a 555 timer used as a Schmitt trigger.

**Fig 1.23**

Pins 4 and 8 are connected to the supply (VCC). The pins 2 and 6 are tied together and the input is given to this common point through a capacitor C. this common point is supplied with an external bias voltage of VCC / 2 with the help of the voltage divider circuit formed by the resistors R1 and R2.

The important characteristic of the Schmitt trigger is Hysteresis. The output of the Schmitt trigger is high if the input voltage is greater than the upper threshold value and the output of the Schmitt trigger is low if the input voltage is lower than the lower threshold value shown fig 1.23

The output retains its value when the input is between the two threshold values. The usage of two threshold values is called Hysteresis and the Schmitt trigger acts as a memory element (a bistable multivibrator or a flip-flop).

The threshold values in this case are 2/3 VCC and 1/3 VCC i.e. the upper comparator trips at 2/3 VCC and the lower comparator trips at 1/3 VCC. The input voltage is compared to these threshold values by the individual comparators and the flip-flop is SET or RESET accordingly. Based on this the output becomes high or low.

When a sine wave of amplitude greater than VCC / 6 is applied at the input, the flipflop is set and reset alternately for the positive cycle and the negative cycle. The output is a square wave and the waveforms for input sine wave and output square wave are shown above.

### **<u>1.11.3 Sequential timer</u>**

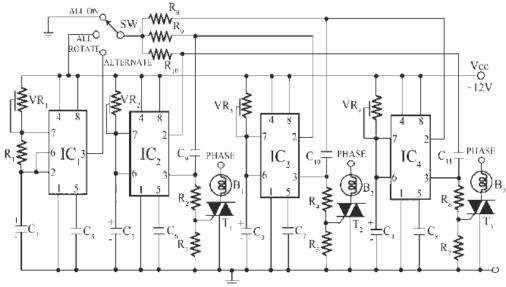

This is a simple sequential timer circuit using NE555 shown fig 1.24 which can be used for psychedelic light, decoration in shops, advertisement boards at night, and in parties. Circuit Description Sequential Timer Using NE555

In the circuit sequential timer circuit IC2, IC3 and IC4 are used as monostable multivibrators. The trigger terminals (pins 2) of these ICs are connected in chain to the previous ICs through RC differentiator network (0.022  $\mu$ F capacitor and 22 K $\Omega$  resistor). IC1 is used as an astable multivibrator with adjustable duty cycle and time period.

To understand the functioning of the sequential timer circuit, supposed the circuit is put in 'all rotate' position and lamp L1 is on. When lamp L1 goes to off state, as pin 3 of IC2 goes to the low state, it triggers IC3 through C9 and R9 differentiator, and thus lamp L2 switches on. In the next period, lamp L2 while going off switches on lamp L3 and so on, thus completing the chain.

### **19 |** Page

**Fig 1.24**

When the switch  $SW_1$  is in 'all on' state, trigger terminal of each  $IC_2$ ,  $IC_3$  and  $IC_4$  is clamped to the ground and thus output of each goes high, making each of the lamp  $L_1$ ,  $L_2$  and  $L_3$  to switch on. This state is useful in checking for the fused lamps.

Since  $IC_1$  is put as astablemultivibrator, when switch  $SW_1$  is put to alternate position, for some time the lamps rotate and then for some time all of them glow simultaneously. For the given component values, the time period can be increased to about four seconds. This time period can be adjusted by  $VR_1$ . The effect on 'alternate' position comes from the facts that in this case trigger terminals of  $IC_2$ ,  $IC_3$  and  $IC_4$  are put to 'all on' and 'all rotate' positions automatically alternately, because output of  $IC_1$  goes to Vcc and ground level alternately. Adjustment of the unit is simple. Put  $SW_1$  to all rotate position and adjust  $VR_2$ ,  $VR_3$  and  $VR_4$  so that each lamp glows for equal time, or the effect is most eye appeasing. Then put the switch to alternate position and adjust  $VR_1$  for most pleasing effect.

If many small lamps are to be used, a suitable sequence for connection of the lamps can be  $L_1 L_2 L_3 L_1 L_2 L_3$ —.

Since the monistable  $IC_2$ ,  $IC_3$  and  $IC_4$  require an initial trigger to being cycling, the circuit may not operates if switch  $SW_1$  is in 'all rotate' position initially. In this case, switch  $SW_1$  to the 'all on' or 'alternate' position momentarily before switching back to the 'all rotate' position.

When the switch SW1 is in 'all on' state, trigger terminal of each IC2, IC3 and IC4 is clamped to the ground and thus output of each goes high, making each of the lamp L1, L2 and L3 to switch on. This state is useful in checking for the fused lamps.

Since IC1 is put as astablemultivibrator, when switch SW1 is put to alternate position, for some time the lamps rotate and then for some time all of them glow simultaneously. For the given component values, the time period can be increased to about four seconds. This time period can be adjusted by VR1.

The effect on 'alternate' position comes from the facts that in this case trigger terminals of IC2, IC3 and IC4 are put to 'all on' and 'all rotate' positions automatically alternately, because output of IC1 goes to Vcc and ground level alternately.

Adjustment of the unit is simple. Put SW1 to all rotate position and adjust VR2, VR3 and VR4 so that each lamp glows for equal time, or the effect is most eye appeasing. Then put the switch to alternate position and adjust VR1 for most pleasing effect.

If many small lamps are to be used, a suitable sequence for connection of the lamps can be L1 L2 L3 L1 L2 L3—.

**20 |** Page

Since the monistable IC2, IC3 and IC4 require an initial trigger to being cycling, the circuit may not operates if switch SW1 is in 'all rotate' position initially. In this case, switch SW1 to the 'all on' or 'alternate' position momentarily can be used as PWM before switching back to the 'all rotate' position.

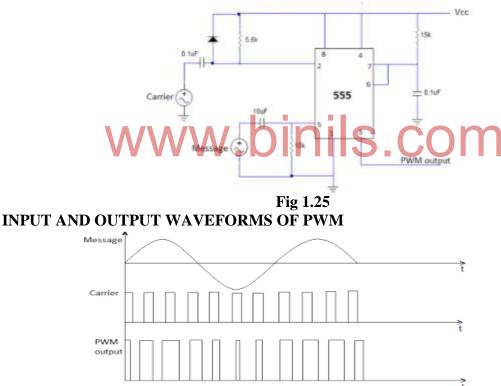

**555 timer can be used as PWM** In analog or digital communication system, it is impossible to transmit a low frequency message signal over a channel, it causes signal distortion, attenuation or signal loss. Inorder to make the transmission ideal (almost), we have to use some techniques called modulation.

**Modulation** can be defined as the process of varying some characteristics of carrier signal in accordance with the instantaneous value of message signal. **Carrier signal** is a high frequency wave generated by a local oscillator, used to carry the message signal from transmitter to reciever. The message signal which is mixed with carrier wave is called modulated signal and the process is called Modulation. The modulation is an important process in a basic communication system, which increases the transmission range, reduces the size of antenna and increases the efficiency of the system by reducing noise interference.

**Pulse width modulation** is a process of varying the width of carrier signal according to the instantaneous amplitude value of message signal. PWM is also known as **Pulse Duration Modulation (PDM) or Pulse Length Modulation (PLM)**. It utilises the advantages of constant amplitude pulses.

**CIRCUIT DIAGRAM OF PWM USING 555 TIMER**

In the circuit diagram shown fig 1.25 the 555 IC is wired as monostable multivibrator, which varies the output period of oscillations according to the amplitude of message signal. That is, Trigger is applied to control the starting time of pulses and modulating signal is fed to control the duration of pulses.

### **Applications of Monostable Multivibrator**

### **Frequency Divider**

**Pulse Width Modulation**

**Linear Ramp Generator**

**21 |** Page

# **REVIEW QUESTIONS**

### Two Mark

| 1  | What is an Operational Amplifier?                                 |

|----|-------------------------------------------------------------------|

| 2  | What are the advantages of Operational Amplifier?                 |

| 3  | Define CMMR.                                                      |

| 4  | Define slew rate.                                                 |

| 5  | Draw the symbol of 741.                                           |

| 6  | What is gain?                                                     |

| 7  | Write the output equation of inverting amplifier.                 |

| 8  | Write the output equation of Non inverting amplifier.             |

| 9  | What is gain of voltage follower?                                 |

| 10 | What is use of voltage follower?                                  |

| 11 | What is the output of summing amplifier if V1 and V2 are inputs.? |

| 12 | What are the input and feedback components of Integrator?         |

| 13 | What are the input and feedback components of Differentiator?     |

| 14 | What is astable mode in 555 time?                                 |

| 15 | What is mono stable mode in 555 time?                             |

| 16 | What is the output of Schmitt trigger?                            |

| 17 | What is PWM?                                                      |

|    |                                                                   |

### Three Mark

| 1  | What are the characteristics of Operational Amplifier? |  |  |  |

|----|--------------------------------------------------------|--|--|--|

| 2  | Draw the block diagram of ideal Operational Amplifier  |  |  |  |

| 3  | Write the parameters of Operational Amplifier          |  |  |  |

| 4  | What is virtual ground?                                |  |  |  |

| 5  | Draw the pin diagram Operational Amplifier 741         |  |  |  |

| 6  | What are the applications of Operational Amplifier?    |  |  |  |

| 7  | Draw the circuit diagram of inverting amplifier.       |  |  |  |

| 8  | Draw the circuit diagram of voltage follower.          |  |  |  |

| 9  | How comparator works?                                  |  |  |  |

| 10 | How zero crossing detector works?                      |  |  |  |

| 11 | Draw the input and output waveforms of Integrator.     |  |  |  |

| 12 | Draw the input and output waveforms of Differentiator. |  |  |  |

### 10 Mark

| 1 | Explain inverting amplifier with circuit diagram and derive its output.           |

|---|-----------------------------------------------------------------------------------|

| 2 | Explain Non inverting amplifier with circuit diagram and derive its output.       |

| 3 | Explain summing amplifier with circuit diagram and derive its output.             |

| 4 | Explain zero crossing detector with circuit diagram , input and output waveforms. |

| 5 | Explain Integrator with circuit diagram and derive its output.                    |

| 6 | Explain Differentiator with circuit diagram and derive its output.                |

| 7 | Explain a stable mode in 555 timer with circuit diagram and derive its output     |

| 8 | Explain mono stable mode in 555 timer with circuit diagram and derive its output  |

| 9 | Explain Schmitt trgger in 555 timer with circuit diagram and derive its output    |

### $\mathbf{UNIT} - \mathbf{II}$

# **BOOLEAN ALGEBRA**

### 2.1 Numbering System

The study of *number systems* is important from the viewpoint of understanding how data are represented before they can be processed by any digital system including a digital computer. It is one of the most basic topics in digital electronics. In this chapter we will discuss different number systems commonly used to represent data. We will begin the discussion with the decimal number system. Although it is not important from the viewpoint of digital electronics, a brief outline of this will be given to explain some of the underlying concepts used in other number systems. This will then be followed by the more commonly used number systems such as the binary, octal and hexadecimal number systems.

The table 2.1 given below shows some examples of number system which are often used in digital circuits.

Table 2.1 examples of number system.

| S.No | Types                 | Base/Radix | Numbers     |

|------|-----------------------|------------|-------------|

| 1    | Decimal number system | 10         | 0,1,2,9     |

| 2    | Binary number system  | 2          | 0,1         |

| 3    | Octal number system   | 8          | 0,1,2,37    |

| 4    | Hexa decimal number   | 16         | 0,1,2,9,    |

|      | system                |            | A,B,C,D,E,F |

### **Decimal Number System**

The decimal system is composed of 10 numerals or symbols. These 10 symbols are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. Using these symbols as digits of a number, we can express any quantity. The decimal system is also called the base-10 system because it has 10 digits

| Weight of each digit | 10 <sup>3</sup>              | 10 <sup>2</sup> | 10 <sup>1</sup> | <b>10<sup>0</sup></b> | 5.0           | 10-1 | <b>10</b> <sup>-2</sup> | <b>10</b> <sup>-3</sup>       |

|----------------------|------------------------------|-----------------|-----------------|-----------------------|---------------|------|-------------------------|-------------------------------|

| Digit value          | =1000                        | =100            | =10             | =1                    | •             | =0.1 | =0.01                   | 0.001                         |

| Bit position         | Most<br>Significant<br>Digit |                 |                 | <u>.</u>              | Decimal point |      |                         | Least<br>Significant<br>Digit |

### **Binary Number System**

In the binary system, there are only two symbols or possible digit values, 0 and 1. This base-2 system can be used to represent any quantity that can be represented in decimal or other base system

| Weight of<br>each digit | 2 <sup>3</sup>                   | $2^2$ | 2 <sup>1</sup> | 2 <sup>0</sup> |                     | 2-1  | 2-2   | 2 <sup>-3</sup>               |

|-------------------------|----------------------------------|-------|----------------|----------------|---------------------|------|-------|-------------------------------|

| Digit value             | =8                               | =4    | =2             | =1             | •                   | =0.5 | =0.25 | =0.125                        |

| Bit<br>position         | Most<br>Signifi<br>cant<br>Digit |       |                |                | Binar<br>y<br>point |      |       | Least<br>Significant<br>Digit |

**Octal Number System**

**23 |** Page

The octal number system has a base of eight, meaning that it has eight possible digits: 0,1,2,3,4,5,6,7

| Weight<br>of each<br>digit | 8 <sup>3</sup>               | <b>8</b> <sup>2</sup> | <b>8</b> <sup>1</sup> | 8 <sup>0</sup> |   | 8-1  | 8-2                        | <b>8</b> <sup>-3</sup> |

|----------------------------|------------------------------|-----------------------|-----------------------|----------------|---|------|----------------------------|------------------------|

| Digit<br>value             | =512                         | =64                   | =8                    | =1             | • | =1/8 | =1/64                      | =1/512                 |

| Bit<br>position            | Most<br>Significant<br>Digit |                       |                       | Octal<br>point |   |      | Least Significant<br>Digit |                        |

### Hexadecimal Number System

The hexadecimal system uses base 16. Thus, it has 16 possible digit symbols. It uses the digits 0 through 9 plus the letters A, B, C, D, E, and F as the 16 digit symbols

| Weight<br>of each<br>digit | 16 <sup>3</sup>              | <b>16</b> <sup>2</sup> | <b>16</b> <sup>1</sup> | <b>16</b> <sup>0</sup> |                          | <b>16<sup>-1</sup></b> | <b>16</b> <sup>-2</sup> | <b>16</b> <sup>-3</sup>       |

|----------------------------|------------------------------|------------------------|------------------------|------------------------|--------------------------|------------------------|-------------------------|-------------------------------|

| Digit<br>value             | =4096                        | =256                   | =16                    | =1                     | •                        | =1/16                  | =1/256                  | =1/4096                       |

| Bit<br>position            | Most<br>Significant<br>Digit |                        |                        |                        | Hexa<br>Decimal<br>point |                        |                         | Least<br>Significant<br>Digit |

### **BCD** Number System

BCD stands for binary coded decimal. A nibble is a string of four bits. BCD numbers express each decimal digit as nibble. It is a decimal number represented in binary form with 0 and 1. In BCD each decimal digit is represented by its four bit binary number. The lowest number is 0000(0) and the highest number is 1001((9)

### 2.2 Conversion from one number system to other

Converting from one code form to another code form is called code conversion, like converting from binary to decimal or converting from hexadecimal to decimal.

Any binary number can be converted to its decimal equivalent simply by summing together the weights of the various positions in the binary number which contain a 1.

### **Binary to Decimal Conversion (Integer)**

### Example 1:

| Binary                                  | Decimal          |

|-----------------------------------------|------------------|

| 110112                                  |                  |

| $(1x2^4)+(1x2^3)+(0x2^2)+(1x2^1)+1x2^0$ | =16+8+0+2+1      |

| Result                                  | 27 <sub>10</sub> |

### Example2:

| Binary                                                          | Decimal              |

|-----------------------------------------------------------------|----------------------|

| 101101012                                                       |                      |

| $(1x2^7)+(0x2^6)+(1x2^5)+(1x2^4)+(0x2^3)+(1x2^2)+(0x2^1)+1x2^0$ | =128+0+32+16+0+4+0+1 |

| Result                                                          | 181 <sub>10</sub>    |

| Example 3:                                  |                                |

|---------------------------------------------|--------------------------------|

| Binary                                      | Decimal                        |

| 0.1101                                      |                                |

| $(1x2^{-1})+(1x2^{-2})+(0x2^{-3})+1x2^{-4}$ | =1x0.5=1x0.25+0x0.125+1x0.0625 |

| Result                                      | 0.8125 10                      |

**Binary-To-Decimal** (fraction)

**Decimal-To-Binary Conversion (Integer)** There are 2 methods:

- Reverse of Binary-To-Decimal Method

- Repeat Division

- **Reverse of Binary-To-Decimal Method**

### **Decimal-To-Binary Conversion (fraction)**

In this case the given decimal number is multiplied by 2 and then records the carry in the integer position. The carry are taken in downward direction( from top to bottom) to obtain the required binary fraction. This process can be stopped either after getting the result as zero or after getting six binary digits.

Convert  $0.85_{10}$  to binary

| Multiplication | Remainder                      | Binary         |

|----------------|--------------------------------|----------------|

| 0.85x2         | = 1.7 = .7 with the carry of 1 | 1              |

| 0.7x2          | = 1.4=.4with the carry of 1    | 1              |

| 0.4x2          | = 0.8 = .8 with the carry of 0 | 0              |

| 0.8x2          | = 1.6 = .6 with the carry of 1 | 1              |

| 0.6x2          | = 1.2 = .2 with the carry of 1 | 1              |

| 0.2x2          | = 0.4 = .4 with the carry of 1 | 1              |

| Result         | $0.85_{10}$                    | $= 0.110110_2$ |

### **Decimal to octal conversion**(Integer)

This method uses repeated division by 8.and writing down the remainder after each division. The remainders are taken in the reverse order(from bottom to top), to form the octal number

### Example1:

Convert 177<sub>10</sub>to octal

| Division | Remainder            | Octal                     |

|----------|----------------------|---------------------------|

| 177/8    | = 22+ remainder of 1 | 1 (Least Significant Bit) |

| 22/8     | = 2 + remainder of 6 | 6                         |

| 2 / 8    | = 0 + remainder of 2 | 2 (Most Significant Bit)  |

| Result   | 177 <sub>10</sub>    | = 261 <sub>8</sub>        |

### **Decimal to octal conversion**(Fraction)

In this case the given decimal number is multiplied by 8 and then records the carry in the integer position. The carry are taken in downward direction (from top to bottom) to obtain the required octal number. This process can be stopped either after getting the result as zero or after getting six digits.

**25** | Page

### Convert 0.8210 to binary

| Multiplication | Remainder                        | Binary         |

|----------------|----------------------------------|----------------|

| 0.82x8         | = 6.56 = .56 with the carry of 6 | 6              |

| 0.56x8         | =4.48=.48 with the carry of 4    | 4              |

| 0.48x8         | = 3.84 = .84 with the carry of 3 | 3              |

| 0.84x8         | = 6.72 = .72 with the carry of 6 | 6              |

| 0.72x8         | = 5.76 = .76 with the carry of 5 | 5              |

| 0.76x8         | = 6.08 = .08 with the carry of 6 | 6              |

| Result         | 0.8510                           | $= 0.643656_8$ |

**Octal to Decimal conversion(Integer)** Any octal number can be converted to its decimal equivalent simply by summing together the weights of the various positions in the octal number

| octal                   | Decimal |  |

|-------------------------|---------|--|

| 1758                    |         |  |

| $1x8^2 + 7x8^1 + 5x8^0$ | 64+56+5 |  |

| Result                  | 12510   |  |

Octal to Decimal conversion(fraction) Decimal to Hexa- decimal conversion

| Binary              | Decimal       |

|---------------------|---------------|

|                     |               |

| 0.458               |               |

| $4x8^{-1}+5x8^{-2}$ | =0.5+0.078125 |

|                     |               |

| Result              | 0.578125 10   |

This method uses repeated division by 16.and writing down the remainder after each division. The remainders are taken in the reverse order (from bottom to top), to form the hexa- decimal number

### **Example1:** Convert 378<sub>10</sub>to hexa-decimal

| Division | Remainder              | Hexa-decimal                |

|----------|------------------------|-----------------------------|

| 378/16   | = 23 + remainder of 10 | A (Least Significant Bit)23 |

| 23/16    | = 1 + remainder of 7   | 7                           |

| 1/16     | = 0 + remainder of 1   | 1 (Most Significant Bit)    |

| Result   | 37810                  | $= 17A_{16}$                |

**Decimal to hexa-decimal conversion(Fraction)** In this case the given decimal number is multiplied by 16 and then records the carry in the integer position. The carry are taken in downward direction (from top to bottom) to obtain the required octal number. This process can be stopped either after getting the result as zero or after getting six digits. Convert  $0.935_{10}$  to hexa-decimal

| Multiplication | Remainder                                | Hexa-decimal      |

|----------------|------------------------------------------|-------------------|

| 0.935x16       | = 14.96 = .96 with the carry of $14(=E)$ | Ε                 |

| 0.96x16        | = 15.36 = .36 with the carry of $15(=F)$ | F                 |

| 0.36x16        | = 5.76 = .76 with the carry of 5         | 5                 |

| 0.76x16        | = $12.16$ =16with the carry of $12$ (=C) | С                 |

| 0.16x16        | = 2.56 = .56 with the carry of 2         | 2                 |

| 0.56x16        | = 8.96 =96 with the carry of 8           | 8                 |

| Result         | 0.93510                                  | $= 0.EF5C28_{16}$ |

**26 |** Page

**Hexa-decimal to decimal conversion** Any Hexa-decimal number can be converted to its decimal equivalent simply by summing together the weights of the various positions in the hexa-decimal number

| octal                                                   | Decimal           |

|---------------------------------------------------------|-------------------|

| 2AF <sub>16</sub>                                       |                   |

| $2 \times (16^2) + 10 \times (16^1) + 15 \times (16^0)$ | 512+160+15        |

| Result                                                  | 687 <sub>10</sub> |

### Hexa-decimal to Decimal conversion(fraction)

| Binary                                       | Decimal           |

|----------------------------------------------|-------------------|

| <b>0.B5</b> <sub>16</sub>                    |                   |

| $Bx16^{-1}+5x16^{-2} = 11x16^{-1}+5x16^{-2}$ | =0.6875+0.0195312 |

|                                              |                   |

| Result                                       | 0.70703112 10     |

### Octal to binary conversion

In octal to binary conversion , each octal digit is converted into its equivalent three digit binary form The octal number and its equivalent three digit binary numbers are shown in table 2.2

| Octal number | Equivalent binary number |        |

|--------------|--------------------------|--------|

| 0            | 000                      |        |

| 1            | 001                      |        |

| 2            | 010                      |        |

| 3            | 011                      |        |

| 4            | 100                      |        |

| 5            | 101                      |        |

| 6            | 110                      |        |

| 7            |                          | IS.COI |

Table 2.2

Convert an octal number326.54 to its equivalent binary number

| octal  | 3   | 2   | 6   |   | 5   | 4   |

|--------|-----|-----|-----|---|-----|-----|

|        |     |     |     | • |     |     |

| Binary | 011 | 010 | 110 |   | 101 | 100 |

|        |     |     |     | • |     |     |

| Octal  | Equivalent    |

|--------|---------------|

| number | binary number |

| 0      | 000           |

| 1      | 001           |

| 2      | 010           |

| 3      | 011           |

| 4      | 100           |

| 5      | 101           |

| 6      | 110           |

| 7      | 111           |

### **Binary to Octal Conversion**

As the binary numbers are comprised of only 0 and 1 in this method, first divide the binary number into group of 3 digits. Suppose the binary numbers are not completed in the form of three digits, sufficient zeros are added to the left most side of the integer part and also

### **27 |** Page

sufficient zeros are added to the right side of fractional part. That means the integer number is arranged in group of three digit from right to left. Conversely, the fraction number is arranged in group of three digit from left to right.

| Binary | 001 | 101 | 001 | •   | 110 | 100 |

|--------|-----|-----|-----|-----|-----|-----|

| octal  | 1   | 5   | 1   | . • | 6   | 4   |

**Example1:**Let us take a binary number say 1101001.11010<sub>2</sub>

### Convert Hexa-decimal numberA26.F4 to its equivalent binary number

| <br>             |      |      | <u> </u> |   |      |      |

|------------------|------|------|----------|---|------|------|

| Hexa-<br>decimal | А    | 2    | 6        |   | F    | 4    |

| decimai          |      |      |          | • |      |      |

|                  |      |      |          | • |      |      |

| Binary           | 1010 | 0010 | 0110     |   | 1111 | 0100 |

| -                |      |      |          |   |      |      |

|                  |      |      |          | • |      |      |

|                  |      |      |          |   |      |      |

### **Binary to Hexa -decimal Conversion**

As the binary numbers are comprised of only 0 and 1 in this method, first divide the binary number into group of 4 digits. Suppose the binary numbers are not completed in the form of four digits, sufficient zeros are added to the left most side of the integer part and also sufficient zeros are added to the right side of fractional part. That means the integer number is arranged in group of four digit from right to left. Conversely, the fraction number is arranged in group of four digit from left to right.

Regroup the binary number by four bits per group starting from LSB if Hexadecimal

# is required. Example1: Let us take a binary number say 1101101001.11010112

| Binary           | 0011 | 0110 | 1001 | • | 1101 | 0110 |

|------------------|------|------|------|---|------|------|

| Hexa-<br>decimal | 3    | 6    | 9    | ٠ | D    | 6    |

### **Decimal to BCD conversion**

In this method each decimal digit is converted into its equivalent 4 digit binary form (BCD) Convert a decimal number 881 to its equivalent BCD number

| Decimal | 8    | 8    | 1`   |

|---------|------|------|------|

| BCD     | 1000 | 1000 | 0001 |

### **BCD to Decimal conversion**

In this method each BCD number in the form of four digit binary pattern is converted into its equivalent decimal number.

| BCD     | 1001 | 1000 | 0001 |

|---------|------|------|------|

| Decimal | 9    | 8    | 1    |

### 2.3 Boolean Algebra

Boolean algebra was invented by world famous mathematician George Boole in the year of 1854. Boolean algebra or switching algebra is a system of mathematical logic to perform different mathematical operations in binary system. These are only two elements 1 and 0 by which all the mathematical operations are to be performed. There only three basis binary operations, AND, OR and NOT by which all simple as well as complex binary

### **28** | Page

mathematical operations are to be done. Some basic logical Boolean operations- AND operation, OR operation, NOT operation,

## 2.4 Basics Laws And Demorgan's Theorems 2.4.1 Basic laws of Boolean Algebra

### 1. OR law

- A + 0 = A where A can be either 0 or 1.

- A + 1 = 1 where A can be either 0 or 1.

- $A + \overline{A} = 1$  where A can be either 0 or 1.

- A + A = A where A can be either 0 or 1.

- 2. AND law  $A \cdot 0 = 0$  where A can be either 0 or 1.

- A  $\cdot$  0 = 0 where A can be either 0 or 1. A  $\cdot$  1 = A where A can be either 0 or 1

- A . A = A where A can be either 0 or 1.

- A .  $\overline{A} = 0$  where A can be either 0 or 1.

### 3. Laws of Complementation

(A')'=A

4. Commutative law

A + B = B + A

A.B=B.A

Here the answer of adding A+B is same as that of B+A. Similarly A.B is same as that of B.A

5. Associative law

# A+(B+C)=(A+B)+C A.(B.C)=(A.B).CVV DINIS COM

6. Distributive law

A+BC=(A+B)(A+C)

A.(B+C)=A.B+A.C

### 7. Some of the following theorems are solved by the basic laws are

- 1.A+AB=A

- 2.A.(A+B)=A

- 3.A+A'B=A+B

- 4.(A+B)(A+B')=A

- 5. AB+AB'=A

### 2.4.2 Demorgan's Theorems

i)

$A + B = A \cdot B$  Demorgan's first theorem states that the complement of a sum equals the product of the complements.

These equalities can be easily proved as shown in truth tables.

| INPUTS |   | LHS |       | RHS |   |     |

|--------|---|-----|-------|-----|---|-----|

| А      | В | A+B | (A+B) | Ā   | B | Ā.Ē |

| 0      | 0 | 0   | 1     | 1   | 1 | 1   |

| 0      | 1 | 1   | 0     | 1   | 0 | 0   |

| 1      | 0 | 1   | 0     | 0   | 1 | 0   |

| 1      | 1 | 1   | 0     | 0   | 0 | 0   |

Table 2.4

(ii)  $\overline{A} \quad \overline{B} = \overline{A} + \overline{B}$

Demorgan's second theorem states that the complement of a product equals the sum of the complement.

| INPUTS |     | LHS |    | RHS         |   |     |

|--------|-----|-----|----|-------------|---|-----|

| А      | BWW | A.B | AB | <b>A</b> CC | B | Ā+B |

| 0      | 0   | 0   | 1  | 1           | 1 | 1   |

| 0      | 1   | 0   | 1  | 1           | 0 | 1   |

| 1      | 0   | 0   | 1  | 0           | 1 | 1   |

| 1      | 1   | 1   | 0  | 0           | 0 | 0   |

Table 2.5

### 2.5 Logic Gates

The basic elements thatmakes up digital system are called as logic gates. The most common logic gates are OR, AND, Not, NAND and NOR gates. OR, AND ,NOT are called fundamental gates. NAND,NOR gates are called as universal gates. Exclusive –OR gate is another logic circuit which can be constructed using and,OR and NOT gate

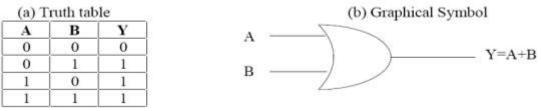

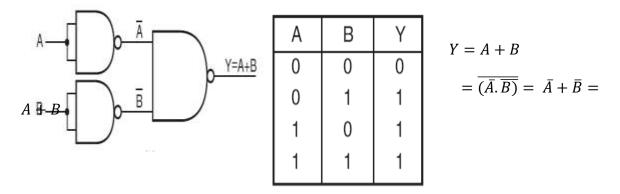

### Logical Addition (OR Gate)

If A and B are the input logic variable and Y is the output Variable, the truth table for a two input OR gate is given in Figure.2.2

The OR gate produces the inclusive – OR function, that is, the output is 1. If input A or input B or both inputs are 1, otherwise the output is a 0. Y=A+B+C+D+E+...

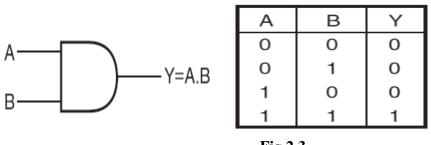

### Logical Multiplication (AND Gate)

The AND gate has one or more inputs and a single output. The output of an AND gate is equal to the multiplication of its inputs. The truth table for a two input AND gate is shown in Figure. The output is 1 if both A and B are 1 and 0 otherwise. In general, in an n input AND gate, only if all the inputs are at logic 1, the output will be 1. That is Y = A,B The Input – Output relationships can be written as

### Fig 2.3

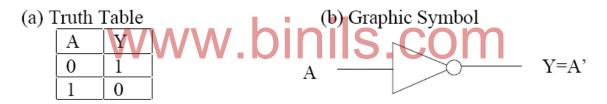

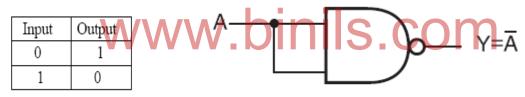

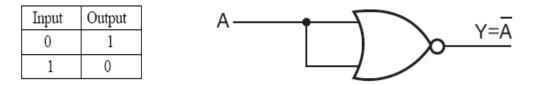

### Logical Inversion: Complement (NOT gate)

The complement function is nothing but inversion, 0 is changed to 1 and 1 to 0. The inverter circuit is also referred to as a NOT gate and it has a single input and single output. The truth table for a NOT gate is shown 2.4

**Fig 2.4**

The NOT logic can be written as, Y=A' or Y=A. The small circle in the output of the graphic symbol of an inverter designates a logic complement.

### **Secondary Gates**

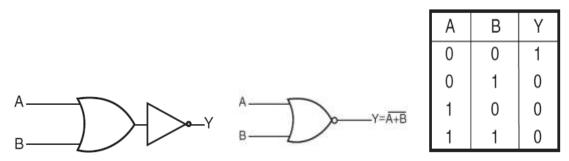

### NOR Gate

The NOR function is the complement of OR function and uses the OR graphic symbol followed by a small circle.

A NOR gate is shown in Figure 2.5 .Figure shows the NOR gate block diagram symbol with inputs A, B, and the output  $\overline{+B}$ . This shows the NOR gate's output will be a 1 only when all the inputs are 0's. If any input represents a 1, then the output of a NOR gate will be a 0.

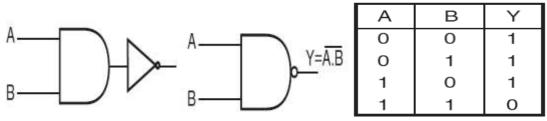

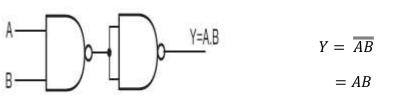

### **NAND Gate**

The NAND function is the complement of the AND function, as indicated by a graphic symbol that consists of an AND graphic symbol followed by a small circle.

If the inputs are A, B then the output of the AND gate will be A.B and the complement of this is (A.B.) A.B as shown in the figure . The truth table for a NAND gate is shown in fig 2.6.

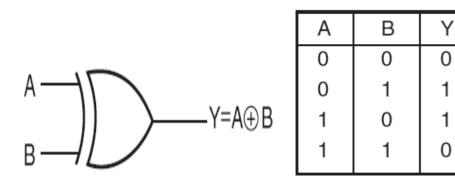

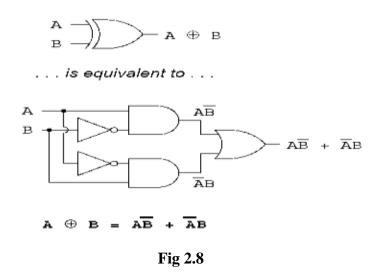

### **EX-OR Gate**

The exclusive-OR gate has a graphical symbol similar to that of the OR gate, except for the additional curved line on the input side. The equivalence, or exclusive-NOR, gate is the complement of the exclusive-OR, as indicated by the small circle on the output side of the graphic symbol.

$Y = (A \oplus B) = \overline{A}B + A\overline{B}$

The exclusive – OR (XOR), denoted by  $\bigoplus$ , is a logical operation that performs the

Following Boolean operation:

Following Boolean operation: It is equal to 1 if only A is equal to 1 or if only y is equal to 1, but not when both are equal to 1, The truth table for a XOR gate is shown in the Figure 2.7 and fig 2.8

Fig 2.7

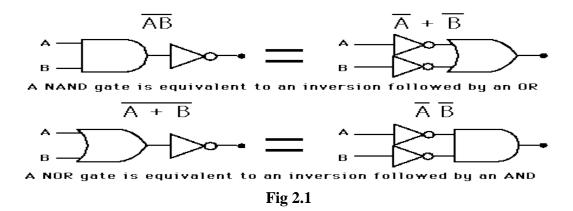

### 2.6 Realization of gates using universal gates NAND and NOR

OR, AND and NOT gates are the three basic logic gates as they together can be used to construct the logic circuit for any given Boolean expression. That is, it is possible to use either only NAND gates or only NOR gates to implement any Boolean expression. This is so because a combination of NAND gates or a combination of NOR gates can be used to perform functions of any of the basic logic gates. It is for this reason that NAND and NOR gates are universal gates.

### NOT gate using NAND gate

NOT gate is constructed using NAND gate by connecting two inputs together as shown in figure 2.9

Fig 2.9

In NOT gate, the output  $Y = \overline{A}$

$$=(\overline{A}.\overline{A})$$

(i.e  $\overline{A}=\overline{A}.\overline{A})$

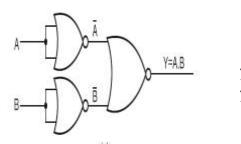

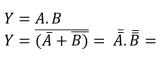

### AND gate using NAND gates

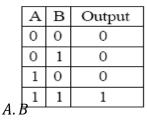

| А | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

Fig 2.10

# <sup>33</sup> | Page www.binils.com Anna University, Polytechnic & Schools

Fig 2.11

### NOT gate using NOR gate

NOT gate is constructed using NAND gate by connecting two inputs together as shown in figure 2.12

In NOT gate, the output Y=A bins.com =(A.A) (i.e A=A.A)

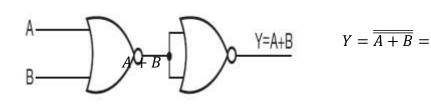

### AND gate using NOR gates

### OR gate using NOR gates

| А | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

Fig 2.14

#### 2.7 Problems using 2,3 and 4 variables

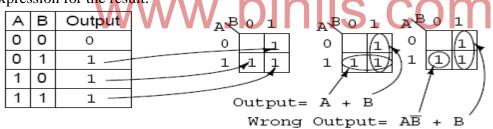

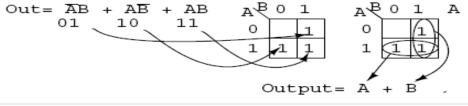

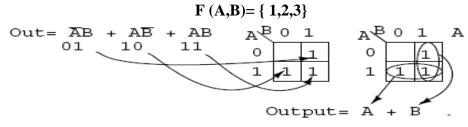

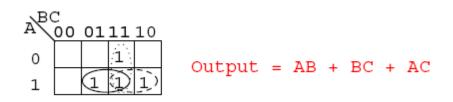

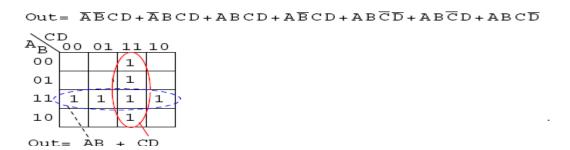

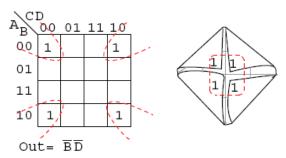

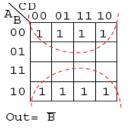

A karnaugh map is a visual display of the fundamental products needed for a sum of products solution. The karnaugh map method provides simple and straight forward procedure to minimize Boolean expressions. in sum of product form. The karnaugh map(k-map) for two, three, four variables are different. The k-map for different variables are discussed below. The map is a diagram made up of squares. Each square represents a **minterm**. **Karnaugh maps reduce logic functions more quickly and easily compared to Boolean algebra**.

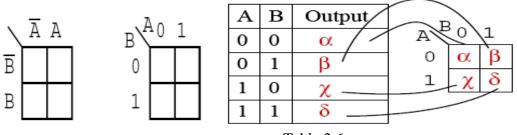

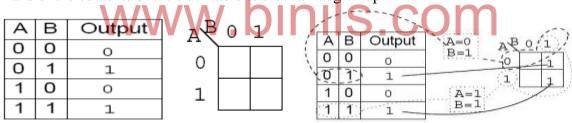

**Two –variables map** Two inputs A and B can take on values of either 0 or 1, high or low, open or closed, True or False, as the case may be. There are **2power2= 4** combinations of inputs producing an output. These four outputs may be recorded in the truth table, or in the Karnaugh map. Look at the Karnaugh map as being a rearranged truth table. The Output of the Boolean equation may be computed by the laws of Boolean algebra and transferred to the truth table or Karnaugh map. If A and B are inputs, then we make a K map as follows

Example:

Transfer the contents of the truth table to the Karnaugh map

In the k-map, first note the variables and their complements The vertical column has A followed by A' and horizontal row has B followed by B'. Then take the combination of inputs, which produce the output as 1. For given truth table output are 1 at A'B and AB input combinations. Enter 1 in the spaces of A'B and AB at the k-map because the corresponding output are high. The remaining spaces are entered with 0s.

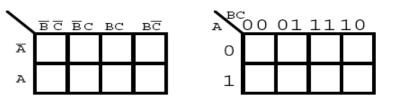

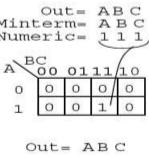

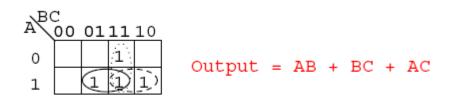

**Three variable k-map** An example of a three variable truth table and their corresponding kmap are shown in fig The horizontal row are labeled as B'C', B'C, BC, BC'. This order is not a binary progress of 00, 01,10 and 11. In the k-map the variables are assigned in a sequence of only one variable changes from complemented to uncomplemented form (or vice versa). The vertical column is marked as A' and A.

#### For 3 variables: 2 power 3 = 8

## <sup>35</sup> | Page www.binils.com Anna University, Polytechnic & Schools

#### **Example :**

| Input |   |   | Output |        |

|-------|---|---|--------|--------|

| Α     | В | С | Y      | M<br>N |

| 0     | 0 | 0 | 0      | IN     |

| 0     | 0 | 1 | 0      | I      |

| 0     | 1 | 0 | 0      |        |

| 0     | 1 | 1 | 0      |        |

| 1     | 0 | 0 | 0      |        |

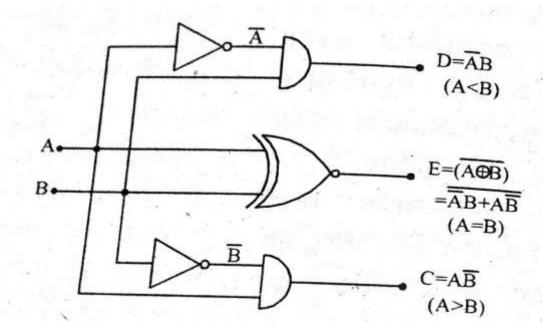

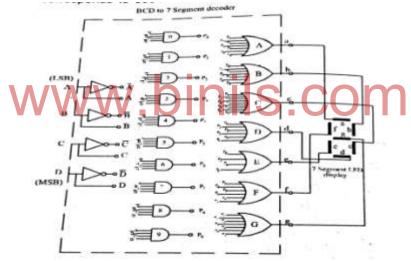

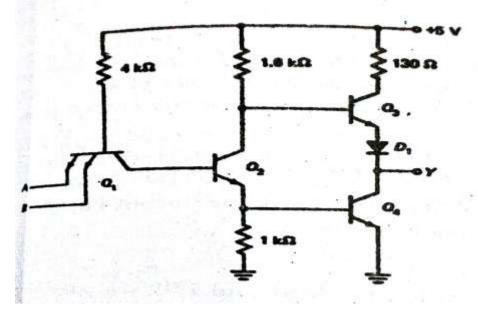

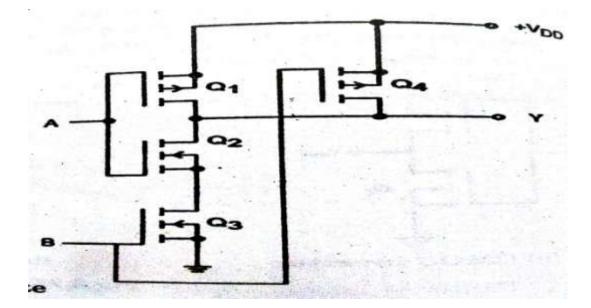

| 1     | 0 | 1 | 0      |        |