## Download Anna University Questions, Syllabus, Notes @ www.AllAbtEngg.com

|     | Reg. No. :                                                                                                                                          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Question Paper Code: 52945                                                                                                                          |

|     | B.E./B.Tech. DEGREE EXAMINATIONS, APRIL/MAY 2019.                                                                                                   |

|     | Third Semester                                                                                                                                      |

|     | Electrical and Electronics Engineering                                                                                                              |

|     | EE 6301 — DIGITAL LOGIC CIRCUITS                                                                                                                    |

|     | (Common to B.E. Electronics and Instrumentation Engineering/B.E. Instrumentation and Control Engineering)                                           |

|     | (Regulation 2013)                                                                                                                                   |

| (4  | Also common to: PTEE 6301 – Digital Logic circuits for B.E. (Part-Time) Third<br>Semester – Electrical and Electronics Engineering Regulation 2014) |

| Tim | e: Three hours Maximum: 100 marks                                                                                                                   |

|     | Answer ALL questions.                                                                                                                               |

|     | PART A — $(10 \times 2 = 20 \text{ marks})$                                                                                                         |

| 1.  | Convert a binary number (1101101)2 to decimal and octal numbers.                                                                                    |

| 2.  | Define Tri-state gates.                                                                                                                             |

| 3.  | Write the logic expression for Full adder and Full subtractor.                                                                                      |

| 4.  | What is meant by canonical form? Give an example for POS and SOP canonical forms.                                                                   |

| 5.  | Draw the sequential logic diagram for Parallel In — Serial Out Shift register.                                                                      |

| 6.  | Write the characteristic equation of JK flip flop and its truth table.                                                                              |

| 7.  | Define race condition. How it can be eliminated.                                                                                                    |

| 8.  | Describe PROM.                                                                                                                                      |

| 9.  | List the purpose of Test bench.                                                                                                                     |

| 10. | Design a Half adder using HDL                                                                                                                       |

|     |                                                                                                                                                     |

## Download Anna University Questions, Syllabus, Notes @ www.AllAbtEngg.com

|     |       | PART B — (5 × 13 = 65 marks)                                                         |                |

|-----|-------|--------------------------------------------------------------------------------------|----------------|

| 11  | . (a) | Define Binary code. Demonstrate the Hamming code with an exa                         | mple.          |

|     |       |                                                                                      | (13)           |

|     |       | Or                                                                                   |                |

|     | (b)   | Explain TTL logic in detail along with its types.                                    | (13)           |

| 12  | . (a) | Design a Combinational logic circuit to convert Binary to Gray                       | anda and       |

|     |       | write its truth table.                                                               | (13)           |

|     |       | . Or                                                                                 |                |

|     | (b)   | Implement the following Boolean function using 4:1 Multiplexer.                      | (20)           |

|     | (0)   | $F(W, X, Y, Z) = \sum m(0, 1, 2, 4, 6, 9, 12, 14)$                                   | (13)           |

|     |       | $\Gamma(n, A, 1, Z) - Z m(0, 1, 2, 4, 0, 3, 12, 14)$                                 |                |

| 13  | . (a) | Synthesis a 3 bit counter using T Flip Flop (State diagram, E                        | xcitation      |

|     |       | table, K-map, Logic diagram).                                                        | (13)           |

|     |       | Or                                                                                   |                |

|     | (b)   | What is meant by a Flip Flop? Write the characteristics e                            |                |

|     |       | characteristics table and draw logic of SR, JK and D flip flops. (2                  | 2+4+4+3)       |

| 14. | . (a) | Explain the steps for the design of Asynchronous sequential circu                    | uits with      |

|     |       | an example.                                                                          | (13)           |

|     |       | Or                                                                                   |                |

|     | (b)   | Draw a PLA circuit to implement the functions                                        | (13)           |

|     |       | $F_1 = AB^{\prime} + AC + A^{\prime} \ BC^{\prime}$ and $F_2 = (AC + BC)^{\prime}$ . |                |

| 15. | . (a) | Describe RTL in HDL with an example.                                                 |                |

|     |       |                                                                                      |                |

|     | 4.    | Or                                                                                   |                |

|     | (b)   | (i) Write the HDL program for 2:1 multiplexer in Dataf<br>Behavioral Description.    | low and<br>(6) |

|     |       | (ii) Write program in HDL to design 2 bit up/down counter.                           |                |

|     |       |                                                                                      | (7)            |

|     |       | 2                                                                                    | 52945          |

|     |       |                                                                                      | . 1            |

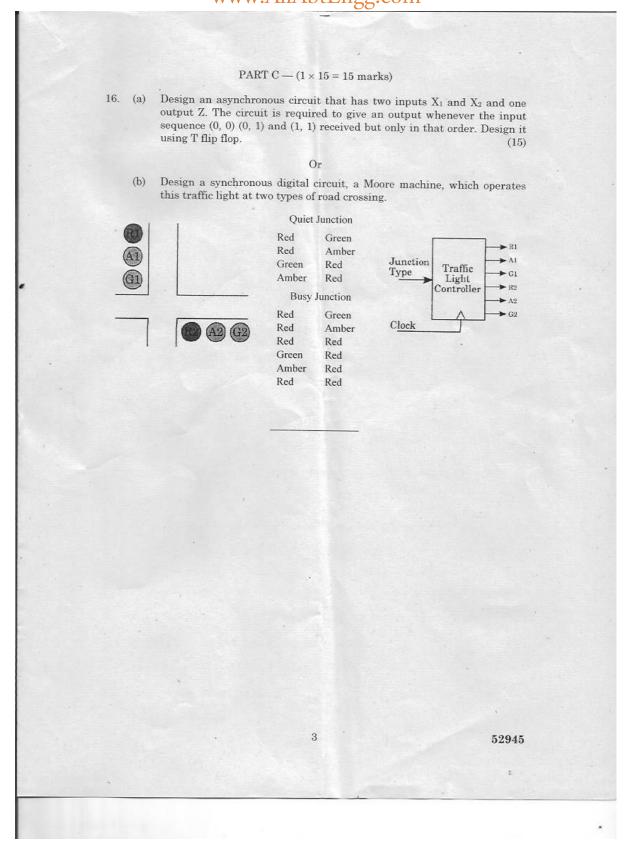

## Download Anna University Questions, Syllabus, Notes @ www.AllAbtEngg.com